# ARM7<sup>TM</sup> Soft IP Support in ProASIC3E ARM7-Ready Devices

### **Features and Benefits**

#### High Capacity

- 600 k to 3 Million System Gates

- 108 k to 504 kbits of True Dual-Port SRAM

- Up to 616 User I/Os

#### Reprogrammable Flash Technology

- 130-nm, 7-Layer Metal (6 Copper), Flash-Based CMOS **Process**

- Live At Power-Up (LAPU) Level 0 Support

- Single-Chip Solution

- Retains Programmed Design When Powered Off

#### On-Chip User Nonvolatile Memory

• 1 kbit of FlashROM (FROM)

#### **High Performance**

- 350 MHz System Performance

- 3.3 V, 66 MHz 64-Bit PCI

#### In-System Programming (ISP) and Security

- Secure ISP Using On-Chip 128-Bit Advanced Encryption Standard (AES) Decryption via JTAG (IEEÉ1532compliant)

FlashLock® to Secure FPGA Contents

#### Low Power

- 1.5 V Core Voltage for Low Power

- Support for 1.5-V-Only Systems

- Low-Impedance Flash Switches

#### **High-Performance Routing Hierarchy**

- Segmented, Hierarchical Routing and Clock Structure

- Ultra-Fast Local and Long-Line Network

- Enhanced High-Speed, Very-Long-Line Network

- High-Performance, Low-Skew Global Network

#### Architecture Supports Ultra-High Utilization

#### Pro (Professional) I/O

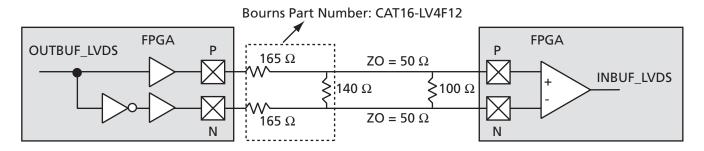

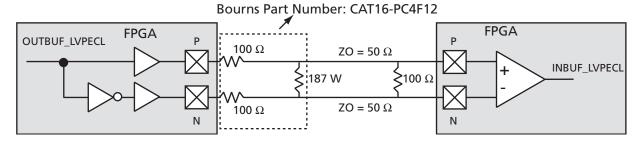

- 700 Mbps DDR, LVDS-Capable I/Os

- 1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation Bank-Selectable I/O Voltages Up to 8 Banks per Chip Single-Ended I/O Standards: LVTTL, LVCMOS 3.3 V/2.5 V/1.8 V/1.5 V, 3.3 V PCI/3.3 V PCI-X, and LVCMOS 2.5 V/5.0 V Input

- Differential I/O Standards: LVPECL and LVDS

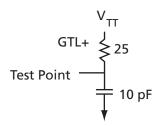

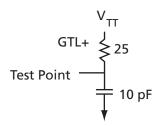

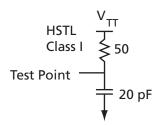

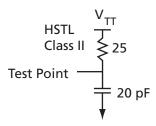

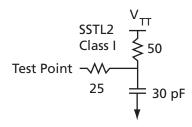

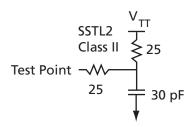

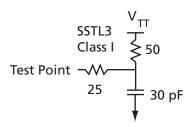

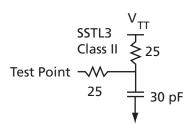

- Voltage-Referenced I/O Standards: GTL+ 2.5 V/3.3 V, GTL 2.5 V/3.3 V, HSTL Class 1 and 2, SSTL2 Class 1 and 2, SSTL3 Class 1 and 2

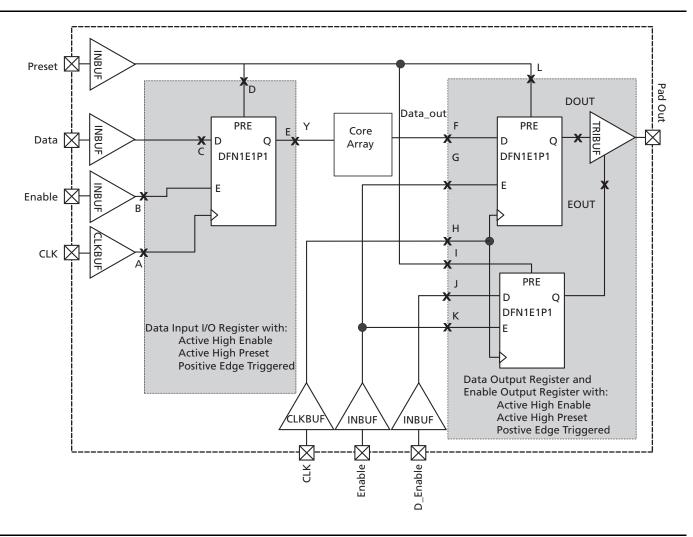

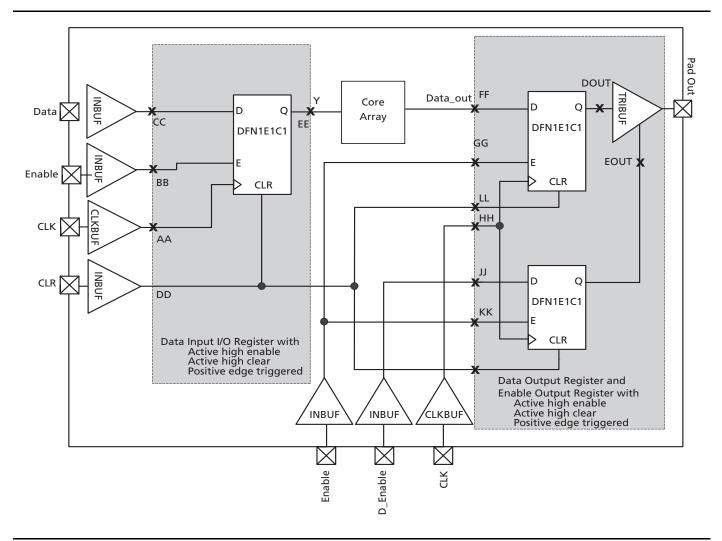

- I/O Registers on Input, Output, and Enable Paths

- Hot-Swappable and Cold Sparing I/Os

- Programmable Output Slew Rate and Drive Strength

- Programmable Input Delay

- Schmitt-Trigger Option on Single-Ended Inputs

- Weak Pull-Up/Down

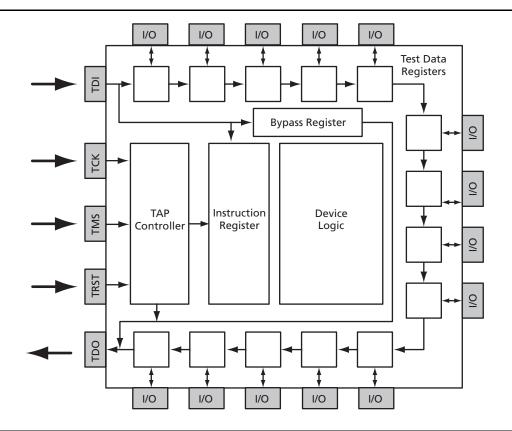

- IEEE1149.1 (JTAG) Boundary Scan Test

- Pin-Compatible Packages Across the ProASIC3E Family

#### Clock Conditioning Circuit (CCC) and PLL

- Six CCC Blocks, Each with an Integrated PLL

- Flexible Phase-Shift, Multiply/Divide, and Delay Capabilities

- Wide Input Frequency Range (1.5 MHz to 350 MHz)

#### SRAMs and FIFOs

- Variable-Aspect Ratio 4,608-Bit RAM Blocks (x1, x2, x4, x9, x18 Organizations Available)

- True Dual-Port SRAM (except x18)

- 24 SRAM and FIFO Configurations with Synchronous Operation up to 350 MHz

#### **ARM7 Processor**

Soft Core Support in ARM7-Ready Devices

Table 1 • **ProASIC3E Product Family**

| ProASIC3E Devices                         | A3PE600               | A3PE1500              | A3PE3000              |

|-------------------------------------------|-----------------------|-----------------------|-----------------------|

| ARM7-Ready ProASIC3E Devices <sup>1</sup> | M7A3PE600             | M7A3PE1500            | M7A3PE3000            |

| System Gates                              | 600 k                 | 1.5 M                 | 3 M                   |

| VersaTiles (D-Flip-Flops)                 | 13,824                | 38,400                | 75,264                |

| RAM kbits (1,024 bits)                    | 108                   | 270                   | 504                   |

| 4,608 Bit Blocks                          | 24                    | 60                    | 112                   |

| FlashROM (FROM) Bits                      | 1 k                   | 1 k                   | 1 k                   |

| Secure (AES) ISP                          | Yes                   | Yes                   | Yes                   |

| CCCs with Integrated PLLs <sup>2</sup>    | 6                     | 6                     | 6                     |

| VersaNet Globals <sup>3</sup>             | 18                    | 18                    | 18                    |

| I/O Banks                                 | 8                     | 8                     | 8                     |

| Maximum User I/Os                         | 270                   | 439                   | 616                   |

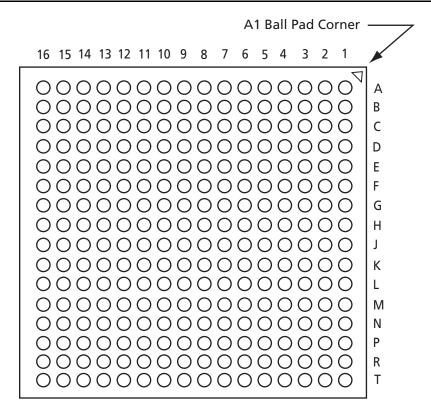

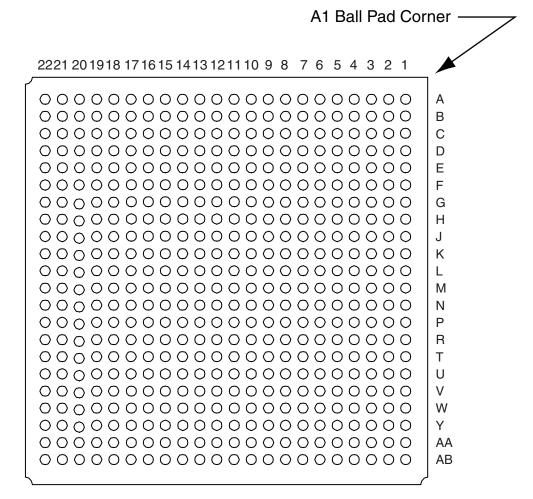

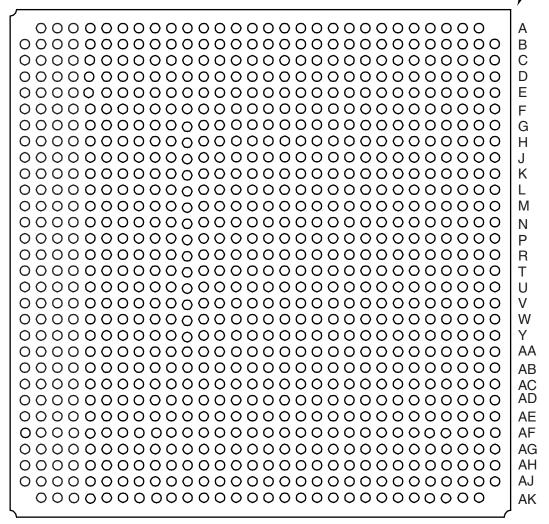

| Package Pins<br>PQFP<br>FBGA              | PQ208<br>FG256, FG484 | PQ208<br>FG484, FG676 | PQ208<br>FG484, FG896 |

#### Notes:

- 1. Refer to the CoreMP7 datasheet for more information.

- The PQ208 package has six CCCs and two PLLs.

- Six chip (main) and three quadrant global networks are available.

- For devices supporting lower densities, refer to the ProASIC3 Flash FPGAs datasheet.

© 2005 Actel Corporation

# I/Os Per Package

| ProASIC3E Devices               | A3PE600                          |                           | АЗРЕ                                                 | 1500 <sup>2</sup> | A3PE3000 <sup>2</sup>            |                           |  |  |

|---------------------------------|----------------------------------|---------------------------|------------------------------------------------------|-------------------|----------------------------------|---------------------------|--|--|

| ARM7-Ready<br>ProASIC3E Devices | М7АЗ                             | PE600                     | M7A3                                                 | PE1500            | M7A3PE3000                       |                           |  |  |

| Package                         | Single-Ended<br>I/O <sup>1</sup> | Differential<br>I/O Pairs | Single-Ended Differential I/O <sup>1</sup> I/O Pairs |                   | Single-Ended<br>I/O <sup>1</sup> | Differential<br>I/O Pairs |  |  |

| PQ208                           | 147                              | 65                        | 147                                                  | 65                | 147                              | 65                        |  |  |

| FG256                           | 165                              | 79                        | -                                                    | _                 | -                                | _                         |  |  |

| FG484                           | 270                              | 135                       | 280                                                  | 136               | 280                              | 136                       |  |  |

| FG676                           | -                                | _                         | 439                                                  | 209               | -                                | _                         |  |  |

| FG896                           | -                                | _                         | _                                                    | _                 | 616                              | 300                       |  |  |

#### Notes:

- 1. Each used differential I/O pair reduces the number of single-ended I/Os available by two.

- 2. For A3PE1500 and A3PE3000 devices, the usage of certain I/O standards is limited as follows:

- SSTL3(I) and (II): up to 40 I/Os per north or south bank

- LVPECL / GTL+ 3.3 V/ GTL 3.3 V: up to 48 I/Os per north or south bank

- SSTL2(I) and (II)/ GTL+ 2.5 V/ GTL 2.5 V: up to 72 I/Os per north or south bank

- 3. FG256 and FG484 are footprint-compatible packages.

- 4. When using voltage-referenced I/O standards, one I/O pin should be assigned as a voltage-referenced pin (V<sub>REF</sub>) per minibank (group of I/Os). Refer to the "I/O Banks and I/O Standards Compatibility" section on page 2-28 for more information about V<sub>REF</sub> and the use of minibanks.

ii Advanced v0.4

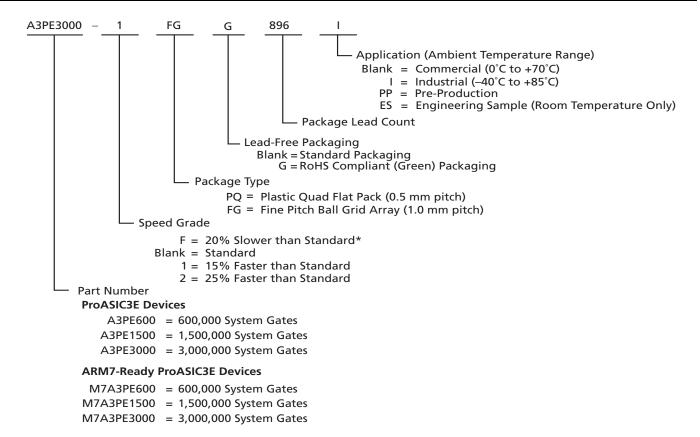

# **ProASIC3E Ordering Information**

**Note:** \*-F Speed Grade – DC and switching based only on simulation. The characteristics are subject to change after establishing FPGA specifications. Some restrictions might be added and will be reflected in future revisions of this document. This speed grade is only supported in commercial temperature range.

# **Temperature Grade Offerings**

|         | A3PE600   | A3PE1500   | A3PE3000   |

|---------|-----------|------------|------------|

| Package | M7A3PE600 | M7A3PE1500 | M7A3PE3000 |

| PQ208   | C, I      | С, І       | С, І       |

| FG256   | C, I      | -          | -          |

| FG484   | C, I      | С, I       | С, І       |

| FG676   | -         | С, І       | -          |

| FG896   | -         | -          | С, І       |

**Note:** C = Commercial Temperature Range: 0°C to 70°C Ambient I = Industrial Temperature Range: -40°C to 85°C Ambient

# **Speed Grade and Temperature Grade Matrix**

|   | -F <sup>3</sup> | Std. | -1 | -2 |

|---|-----------------|------|----|----|

| С | ✓               | ✓    | ✓  | ✓  |

| I | -               | ✓    | ✓  | ✓  |

#### Notes:

- 1. C = Commercial Temperature Range: 0°C to 70°C Ambient

- 2. I = Industrial Temperature Range: -40°C to 85°C Ambient

- 3. DC and switching characteristics for –F speed grade targets based only on simulation.

The characteristics provided for –F speed grade are subject to change after establishing FPGA specifications. Some restrictions might be added and will be reflected in future revisions of this document. The –F speed grade is only supported in commercial temperature range.

Datasheet references made to ProASIC3E devices also apply to ARM7-ready ProASIC3E devices. The part numbers start with M7.

Contact your local Actel representative for device availability (http://www.actel.com/contact/offices/index.html).

Advanced v0.4

# **Table of Contents**

| Introduction and Overview               |   |

|-----------------------------------------|---|

| General Description 1-                  | 1 |

| Related Documents                       | 7 |

| Device Architecture                     |   |

| Introduction                            | 1 |

| Device Overview                         |   |

| Pin Descriptions                        |   |

| Software Tools                          |   |

| Programming                             |   |

| Security                                |   |

| ISP                                     |   |

|                                         | , |

| DC and Switching Characteristics        |   |

| General Specifications                  | 1 |

| Calculating Power Dissipation           | 5 |

| User I/O Characteristics                |   |

| VersaTile Characteristics               | 9 |

| Global Resource Characteristics         | 3 |

| Embedded SRAM and FIFO Characteristics  | 5 |

| Embedded FROM Characteristics           | 5 |

| JTAG 1532 Characteristics               | 5 |

|                                         |   |

| Package Pin Assignments                 |   |

| 208-Pin PQFP                            | 1 |

| 256-Pin FBGA                            | 3 |

| 484-Pin FBGA                            | 2 |

| 676-Pin FBGA                            | 8 |

| 896-Pin FBGA                            | 9 |

| Datasheet Information                   |   |

| List of Changes                         | 1 |

| Datasheet Categories 5-7                |   |

| Export Administration Regulations (FAR) |   |

Advanced v0.4

# **Introduction and Overview**

# **General Description**

ProASIC3E, the third-generation family of Actel Flash FPGAs, offers performance, density, and features beyond those of the ProASIC<sup>PLUS®</sup> family. The nonvolatile Flash technology gives ProASIC3E devices the advantage of being a secure, low-power, single-chip solution that is live at power-up. ProASIC3E is reprogrammable and offers time-to-market benefits at an ASIC-level unit cost. These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

ProASIC3E devices offer 1 kbit of on-chip, programmable, nonvolatile FlashROM (FROM) memory storage as well as clock conditioning circuitry based on six integrated phase-locked loops (PLLs). ProASIC3E devices have up to 3 million system gates, supported with up to 504 kbits of true dual-port SRAM and up to 616 user I/Os.

All ProASIC3E devices support the ARM7 soft IP core, and the ARM7-ready devices have Actel ordering numbers that begin with M7A3PE.

# Flash Advantages

#### **Reduced Cost of Ownership**

Advantages to the designer extend beyond low-unit cost, performance, and ease of use. Unlike SRAM-based FPGAs, the Flash-based ProASIC3E devices allow for all functionality to be live at power-up; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system reprogramming to support future design iterations and field upgrades with confidence that valuable intellectual property (IP) cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The ProASIC3E family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the ProASIC3E family a costeffective ASIC replacement solution, especially for applications in the consumer, networking/ communications, computing, and avionics markets.

#### Security

The nonvolatile, Flash-based ProASIC3E devices require no boot PROM, so there is no vulnerable external bitstream that can be easily copied. ProASIC3E devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile, Flash programming can offer.

ProASIC3E devices utilize a 128-bit Flash-based lock and a separate AES key to secure programmed intellectual property and configuration data. In addition, all FROM data in the ProASIC3E devices can be encrypted prior to loading, using the industry-leading AES-128 (FIPS192) bit block cipher encryption standard. The AES standard was adopted by the National Institute of Standards and Technology (NIST) in 2000, and replaces the 1977 DES standard. ProASIC3E devices have a built-in AES decryption engine and a Flash-based AES key that make them the most comprehensive programmable logic device security solution available today. ProASIC3E devices with AES-based security allow for secure, remote field updates over public networks such as the Internet, and ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves. The contents of a programmed ProASIC3E device cannot be read back, although secure design verification is possible.

Security, built into the FPGA fabric, is an inherent component of the ProASIC3E family. The Flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. ProASIC3E, with FlashLock and AES security, is unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected and secure, making remote ISP possible. A ProASIC3E device provides the most impenetrable security for programmable logic designs.

# **Single Chip**

Flash-based FPGAs store the configuration information in on-chip Flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, Flash-based ProASIC3E FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load the device configuration data. This reduces bill-of-materials costs and printed circuit board (PCB) area, and increases security and system reliability.

#### Live at Power-Up

The Actel Flash-based ProASIC3E devices support Level 0 of the live at power-up (LAPU) classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The LAPU feature of Flash-based ProASIC3E devices greatly simplifies total system design and reduces total system cost, often eliminating the need for Complex Programmable Logic Devices (CPLDs) and clock generation PLLs that are used for this purpose in a system. In addition, glitches and brownouts in system power will not corrupt the ProASIC3E device's Flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based ProASIC3E devices simplify total system design, and reduce cost and design risk, while increasing system reliability and improving system initialization time.

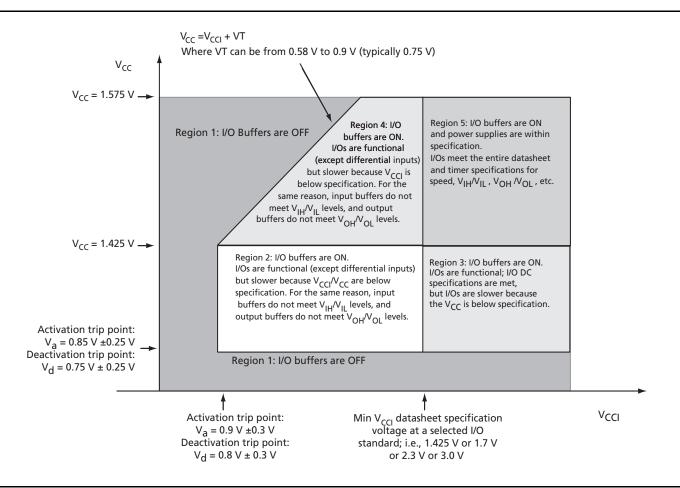

Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section on page 3-3.

#### **Firm Errors**

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of ProASIC3E Flash-based FPGAs. Once it is programmed, the Flash cell configuration element of ProASIC3E FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

#### **Low Power**

Flash-based ProASIC3E devices exhibit power characteristics similar to an ASIC, making them an ideal choice for power-sensitive applications. ProASIC3E devices have only a very limited power-on current surge, and no high-current transition period, both of which occur on many FPGAs.

ProASIC3E devices also have low dynamic power consumption to further maximize power savings.

### **Advanced Flash Technology**

The ProASIC3E family offers many benefits, including nonvolatility and reprogrammability through an advanced Flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant Flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

#### **Advanced Architecture**

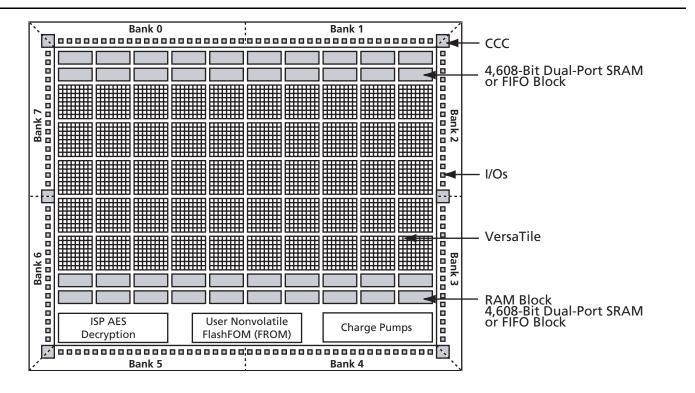

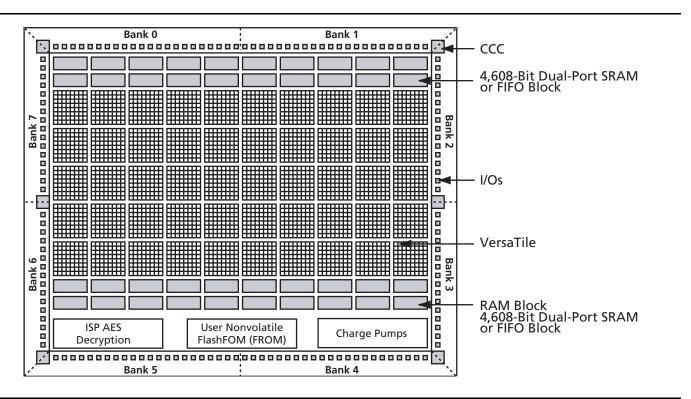

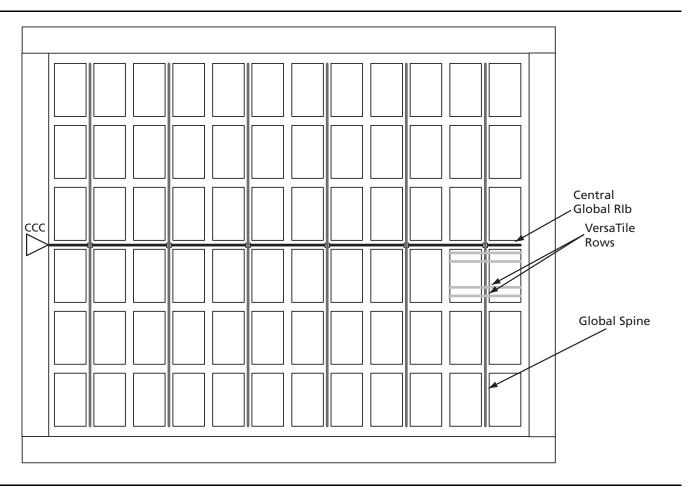

The proprietary ProASIC3E architecture provides granularity comparable to standard-cell ASICs. The ProASIC3E device consists of five distinct and programmable architectural features (Figure 1-1 on page 1-3):

- FPGA VersaTiles

- Dedicated FlashROM (FROM) memory

- Dedicated SRAM/FIFO memory

- Extensive clock conditioning circuitry (CCC) and PLLs

- Pro I/O structure

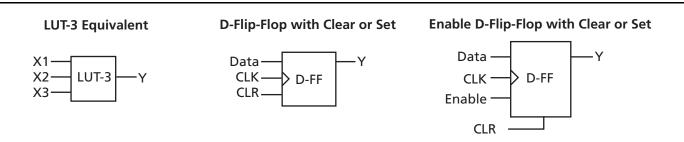

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function or as a D-flip-flop (with or without enable), or as a latch by programming the appropriate Flash switch interconnections. The versatility of the ProASIC3E core tile as either a three-input look-up-table (LUT) equivalent or as a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the Actel ProASIC families of Flash-based FPGAs. VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

In addition, extensive on-chip programming circuitry allows for rapid, single-voltage (3.3 V) programming of the ProASIC3E devices via an IEEE1532 JTAG interface.

1-2 Advanced v0.4

Figure 1-1 • Device Architecture Overview ProASIC3E

#### **VersaTiles**

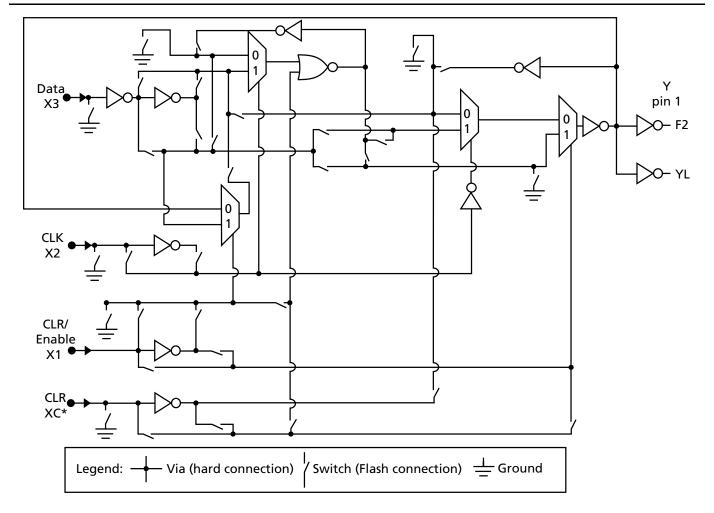

The ProASIC3E core consists of VersaTiles, which have been enhanced from the ProASIC<sup>PLUS</sup> core tiles. The ProASIC3E VersaTile supports the following:

- All three-input logic functions LUT-3 equivalent

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-2 for VersaTile configurations.

For more information about VersaTiles, refer to the "VersaTile" section on page 2-2.

Figure 1-2 • VersaTile Configurations

#### **User Nonvolatile FlashROM (FROM)**

Actel ProASIC3E devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM (FROM). The FROM can be used in diverse system applications:

- Internet protocol addressing (wireless or fixed)

- System calibration settings

- Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- Secure key storage for secure communications algorithms

- Asset management/tracking

- · Date stamping

- Version management

The FROM is written using the standard ProASIC3E IEEE1532 JTAG programming interface. The core can be individually programmed (erased and written), and onchip AES decryption can be used selectively to securely load data over public networks, such as security keys stored in the FROM for a user design.

The FROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FROM can ONLY be programmed from the JTAG interface, and cannot be programmed from the internal logic array.

The FROM is programmed as 8 banks of 128 bits; however, reading is performed on a random byte-by-byte basis. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FROM address determine the bank, and the four least significant bits (LSBs) of the FROM address define the byte.

The Actel ProASIC3E development software solutions, Libero® Integrated Design Environment (IDE) and Designer v6.1 or later, have extensive support for the FROM memory. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. The second part allows the inclusion of static data for system version control. Data for the FROM can be generated quickly and easily using Actel Libero IDE and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FROM contents.

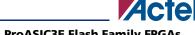

#### **SRAM and FIFO**

ProASIC3E devices have embedded SRAM blocks along the north and south sides of the device. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256x18, 512x9, 1kx4, 2kx2, or 4kx1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be sent through a 4-bit port and read as a single bitstream. The embedded SRAM blocks can be initialized via the device JTAG port (ROM emulation mode), using the UJTAG macro. For more information, refer to the application note, *UJTAG Applications in ProASIC3/E Devices*.

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost-Empty (AEMPTY) and Almost-Full (AFULL) flags in addition to the normal Empty and Full flags. The embedded FIFO control unit contains the counters necessary for the generation of the read and write address pointers. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

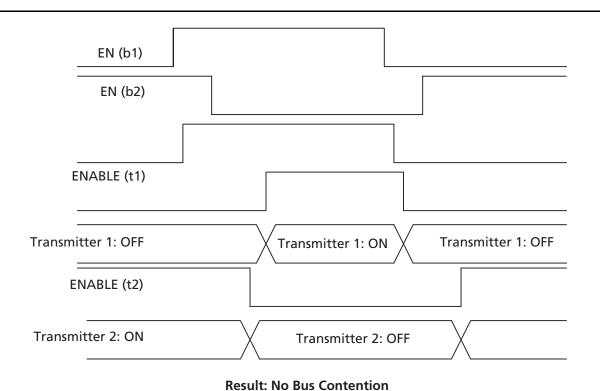

#### PLL and Clock Conditioning Circuitry (CCC)

ProASIC3E devices provide designers with very flexible clock conditioning capabilities. Each member of the ProASIC3E family contains six CCCs, each with an integrated PLL.

The six CCC blocks are located in the four corners and the centers of the east and west sides.

To maximize user I/Os, only the center east and west PLLs are available in devices using the PQ208 package. However, all six CCC blocks are still usable; the four corner CCCs allow simple clock delay operations as well as clock spine access (refer to the "Clock Conditioning Circuits" section on page 2-13 for more information).

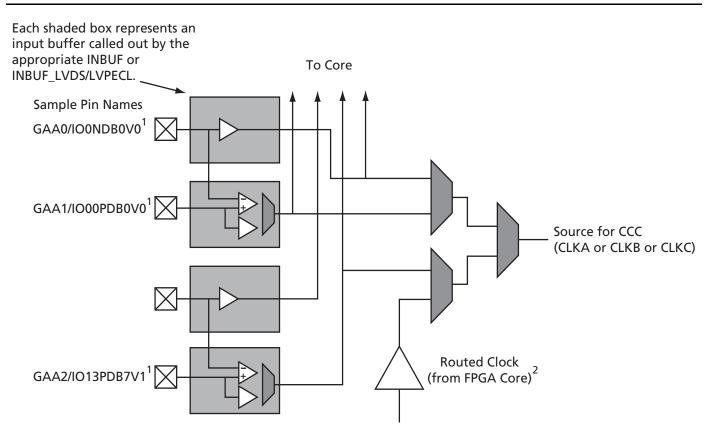

The inputs of the six CCC blocks are accessible from the FPGA core or from one of several I/O inputs located near the CCC that have dedicated connections to the CCC block.

1-4 Advanced v0.4

The CCC block has the following key features:

- Wide input frequency range (f<sub>IN\_CCC</sub>) = 1.5 MHz to 350 MHz

- Output frequency range (f<sub>OUT\_CCC</sub>) = 0.75 MHz to 350 MHz

- Clock delay adjustment via programmable and fixed delays from -7.56 ns to +11.12 ns

- Two programmable delay types; refer to Figure 2-16 on page 2-17, Table 2-4 on page 2-18, and the "Features Supported on Every I/O" section on page 2-31 for more information.

- Clock skew minimization

- Clock frequency synthesis

#### Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°.

Output phase shift depends on the output divider configuration.

- Output duty cycle =  $50\% \pm 1.5\%$  or better

- Low output jitter: worst case < 2.5% x clock period peak-to-peak period jitter when single global network used

- Maximum acquisition time = 150 μs

- Low power consumption of 5 mW

- Exceptional tolerance to input period jitter allowable input jitter is up to 1.5 ns

- Four precise phases; maximum misalignment between adjacent phases of 40 ps x (350 MHz / fout\_ccc)

#### **Global Clocking**

ProASIC3E devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there is a comprehensive global clock distribution network.

Each VersaTile input and output port has access to nine VersaNets: six chip (main) and three quadrant global networks (Figure 2-9 on page 2-9). The VersaNets can be driven by the CCC or directly accessed from the core via multiplexers (MUXes). The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

#### Pro I/Os with Advanced I/O Standards

The ProASIC3E family of FPGAs features a flexible I/O structure, supporting a range of voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V). ProASIC3E FPGAs support 19 different I/O standards, including single-ended, differential, and voltage-referenced. For more information, see Table 2-23 on page 2-48.

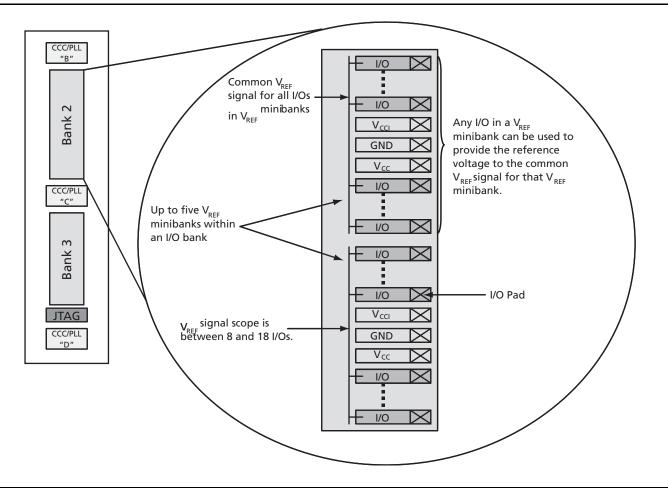

The I/Os are organized into banks, with eight banks per device (two per side). The configuration of these banks determines the I/O standards supported (see Table 2-14 on page 2-30 for more information). Each I/O bank is subdivided into  $V_{REF}$  minibanks, which are used by voltage-referenced I/Os.  $V_{REF}$  minibanks contain 8 to 18 I/Os. All the I/Os in a given minibank share a common  $V_{REF}$  line. Therefore, if any I/O in a given  $V_{REF}$  minibank is configured as a  $V_{REF}$  pin, the remaining I/Os in that minibank will be able to use that reference voltage.

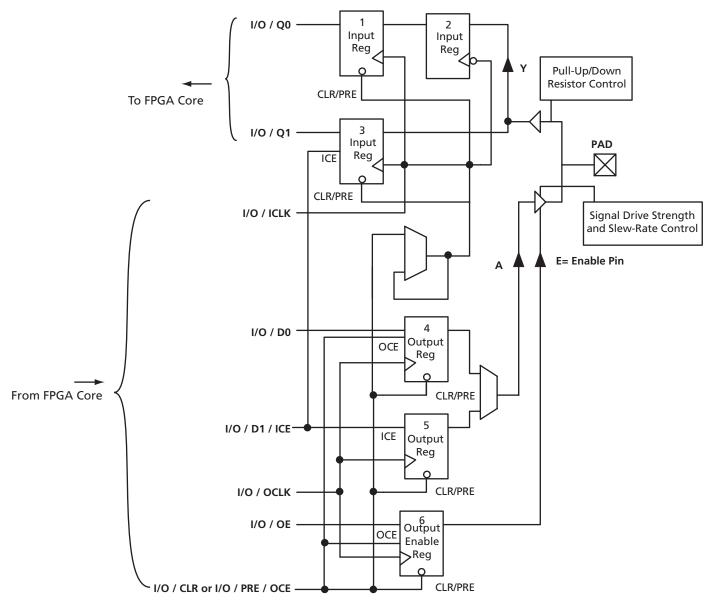

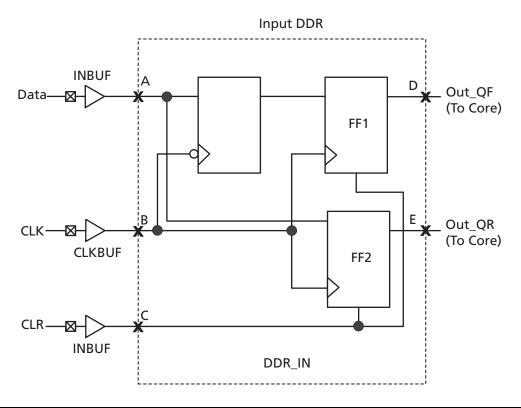

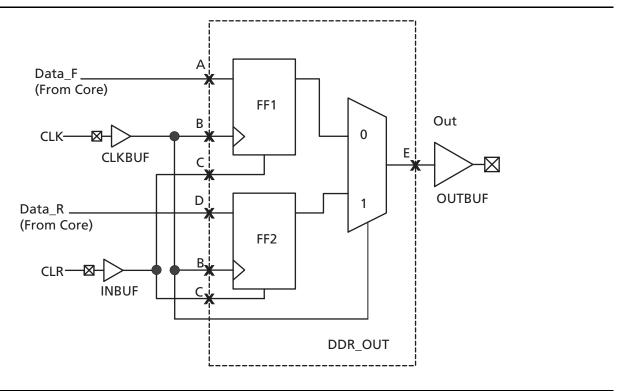

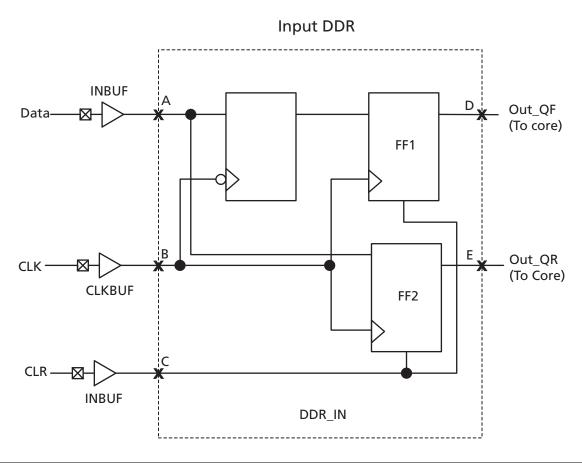

Each I/O module contains several input, output, and enable registers (Figure 2-23 on page 2-33). These registers allow the implementation of the following:

- Single-Data-Rate applications (e.g., PCI 66 MHz, bidirectional SSTL 2 and 3, Class I and II)

- Double-Data-Rate applications (e.g., DDR LVDS I/O for point-to-point communications and DDR 200 MHz SRAM using bidirectional HSTL Class II – "DDR Module Specifications" section on page 3-55)

## **Related Documents**

### **Application Notes**

In-System Programming (ISP) in ProASIC3/E Using FlashPro3

http://www.actel.com/documents/PA3\_E\_ISP\_AN.pdf

ProASIC3/E FlashROM (FROM)

http://www.actel.com/documents/PA3\_E\_FROM\_AN.pdf

ProASIC3/E Security

http://www.actel.com/documents/PA3\_E\_Security\_AN.pdf

ProASIC3/E SRAM/FIFO Blocks

http://www.actel.com/documents/PA3\_E\_SRAMFIFO\_AN.pdf

Programming a ProASIC3/E Using a Microprocessor

http://www.actel.com/documents/PA3\_E\_Microprocessor\_AN.pdf

UJTAG Applications in ProASIC3/E Devices

http://www.actel.com/documents/PA3\_E\_UJTAG\_AN.pdf

Using DDR for ProASIC3/E Devices

http://www.actel.com/documents/PA3\_E\_DDR\_AN.pdf

Using Global Resources in Actel ProASIC3/E Devices

http://www.actel.com/documents/PA3\_E\_Global\_AN.pdf

Power-Up/Down Behavior of ProASIC3/E Devices

http://www.actel.com/documents/ProASIC3 E PowerUp AN.pdf

For additional ProASIC3E application notes, go to http://www.actel.com/techdocs/appnotes/products.aspx.

#### **User's Guides**

ACTgen Cores Reference Guide

http://www.actel.com/documents/gen\_refguide.pdf

Designer User's Guide

http://www.actel.com/documents/designerUG.pdf

ProASIC3/E Macro Library Guide

http://www.actel.com/documents/pa3\_libguide.pdf

1-6 Advanced v0.4

# **Device Architecture**

## Introduction

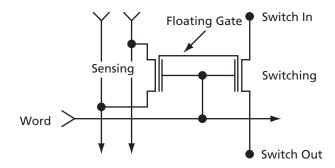

# Flash Technology

#### **Advanced Flash Switch**

Unlike SRAM FPGAs, the ProASIC3E family uses a live on power-up ISP Flash switch as its programming element. Flash cells are distributed throughout the device to provide nonvolatile, reconfigurable programming to connect signal lines to the appropriate VersaTile inputs and outputs. In the Flash switch, two transistors share the floating gate, which stores the programming

information (Figure 2-1). One is the sensing transistor, which is only used for writing and verification of the floating gate voltage. The other is the switching transistor. The latter is used to connect or separate routing nets, or to configure VersaTile logic. It is also used to erase the floating gate. Dedicated high-performance lines are connected as required using the Flash switch for fast, low-skew, global signal distribution throughout the device core. Maximum core utilization is possible for virtually any design. The use of the Flash switch technology also removes the possibility of firm errors, which are increasingly common in SRAM-based FPGAs.

Figure 2-1 • ProASIC3E Flash-Based Switch

### **Device Overview**

The ProASIC3E device family consists of five distinct programmable architectural features (Figure 2-2):

- FPGA fabric/core (VersaTiles)

- Routing and clock resources (VersaNets)

- FlashROM (FROM) memory

- Dedicated SRAM/FIFO memory

- Pro I/O structure

#### **Core Architecture**

#### VersaTile

The proprietary ProASIC3E family architecture provides granularity comparable to gate arrays. The ProASIC3E device core consists of a sea-of-VersaTiles architecture.

As illustrated in Figure 2-3 on page 2-3, there are four inputs in a logic VersaTile cell, and each VersaTile can be configured using the appropriate Flash switch connections:

- Any three-input logic function

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set (on a fourth input)

VersaTiles can flexibly map the logic and sequential gates of a design. The inputs of the VersaTile can be inverted (allowing bubble pushing), and the output of the tile can connect to high-speed, very-long-line routing resources. VersaTiles and larger functions are connected with any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, the SET/CLR is supported by a fourth input. The fourth input is routed to the core cell over the VersaNet (global) network.

The SET/CLR signal can only be routed to this fourth input over the VersaNet (global) network. However, if in the user design, the SET/CLR signal is not routed over the VersaNet network, a compile warning message will be given and the intended logic function will be implemented by two VersaTiles instead of one.

The output of the VersaTile is F2 when the connection is to the ultra-fast local lines, or YL when the connection is to the efficient long-lines or very-long-lines resources.

Figure 2-2 • Device Architecture Overview ProASIC3E

2-2 Advanced v0.4

*Note:* \*This input can only be connected to the global clock distribution network. Figure 2-3 • ProASIC3E Core VersaTile

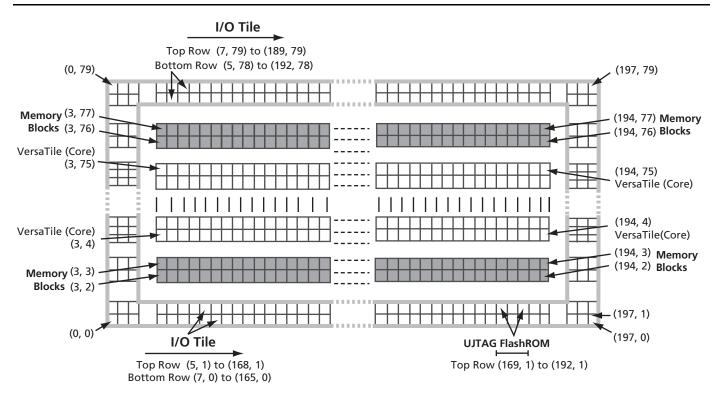

#### **Array Coordinates**

During many place-and-route operations in the Actel Designer software tool, it is possible to set constraints that require array coordinates. Table 2-1 is provided as a reference. The array coordinates are measured from the lower left (0, 0). They can be used in region constraints for specific logic groups/blocks, designated by a wildcard, and can contain core cells, memories, and I/Os.

Table 2-1 provides array coordinates of core cells and memory blocks.

I/O and cell coordinates are used for placement constraints. Two coordinate systems are needed because there is not a one-to-one correspondence between I/O cells and core cells. In addition, the I/O coordinate system

changes depending on the die/package combination. It is not listed in Table 2-1. The Designer ChipPlanner tool provides array coordinates of all I/O locations. I/O and cell coordinates are used for placement constraints. However, I/O placement is easier by package pin assignment.

Figure 2-4 illustrates the array coordinates of an A3PE600 device. For more information on how to use array coordinates for region/placement constraints, see the *Designer User's Guide* or online help (available in the software) for ProASIC3E software tools.

**Table 2-1** • **ProASIC3E Array Coordinates**

|          | VersaTiles Memory Rows |     |      |     |                  |                      | All    |            |  |  |  |

|----------|------------------------|-----|------|-----|------------------|----------------------|--------|------------|--|--|--|

|          | М                      | in. | Max. |     | Bottom           | Bottom Top           |        | Max.       |  |  |  |

| Device   | ж                      | У   | х    | У   | (x, y)           | (x, y)               | (x, y) | (x, y)     |  |  |  |

| A3PE600  | 3                      | 4   | 194  | 75  | (3, 2)           | (3, 76)              | (0, 0) | (197, 79)  |  |  |  |

| A3PE1500 | 3                      | 4   | 322  | 123 | (3, 2)           | (3, 124)             | (0, 0) | (325, 127) |  |  |  |

| A3PE3000 | 3                      | 6   | 450  | 173 | (3, 2) or (3, 4) | (3, 174) or (3, 176) | (0, 0) | (453, 179) |  |  |  |

**Note:** The vertical I/O tile coordinates are not shown. West side coordinates are {(0, 2) to (2, 2)} to {(0, 77) to (2, 77)}; east side coordinates are {(195, 2) to (197, 2)} to {(195, 77) to (197, 77)}.

Figure 2-4 • Array Coordinates for A3PE600

#### **Routing Architecture**

#### **Routing Resources**

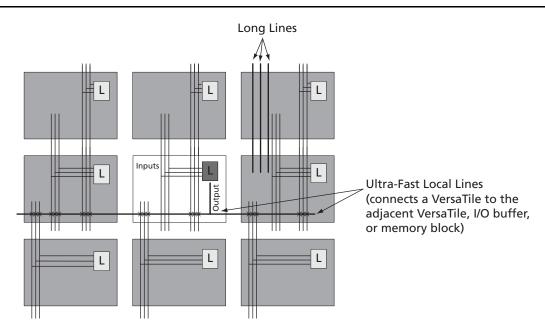

The routing structure of ProASIC3E devices is designed to provide high performance through a flexible four-level hierarchy of routing resources: ultra-fast local resources, efficient long-line resources, high-speed, very-long-line resources, and the high-performance VersaNet networks.

The ultra-fast local resources are dedicated lines that allow the output of each VersaTile to connect directly to every input of the eight surrounding VersaTiles (Figure 2-5). The exception to this is that the SET/CLR input of a VersaTile configured as a D-type flip-flop is driven only by the VersaTile global network.

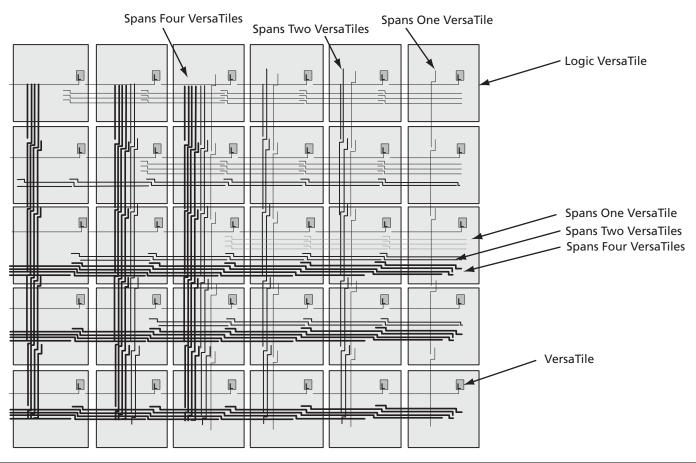

The efficient, long-line resources provide routing for longer distances and higher fanout connections. These resources vary in length (spanning 1, 2, or 4 VersaTiles), run both vertically and horizontally, and cover the entire ProASIC3E device (Figure 2-6 on page 2-6). Each VersaTile can drive signals onto the efficient long-line resources, which can access every input of every VersaTile. Active buffers are inserted automatically by routing software to limit the loading effects.

The high-speed, very-long-line resources, which span the entire device with minimal delay, are used to route very long or high-fanout nets: length +/-12 VersaTiles in the vertical direction and length +/-16 in the horizontal direction from a given core VersaTile (Figure 2-7 on page 2-7). Very long lines in ProASIC3E devices have been enhanced over those in previous ProASIC families. This provides a significant performance boost for long-reach signals.

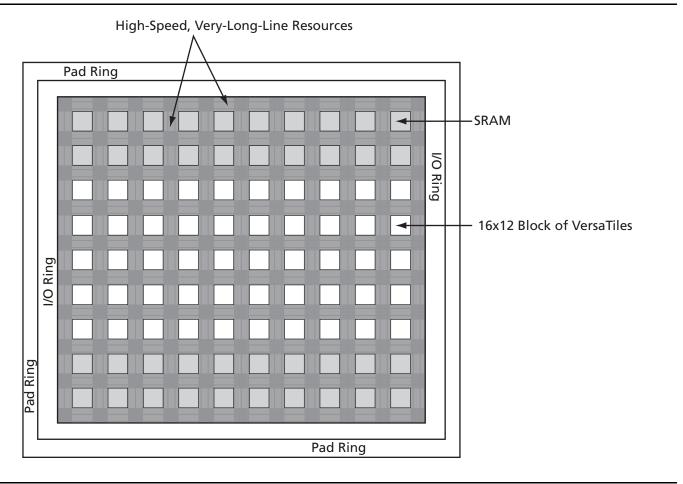

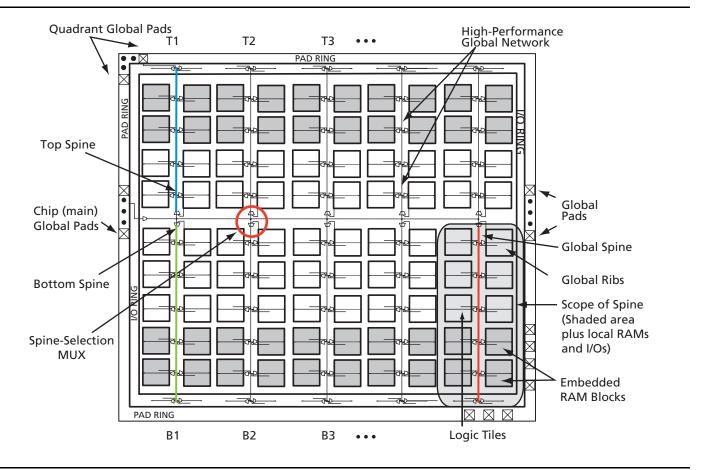

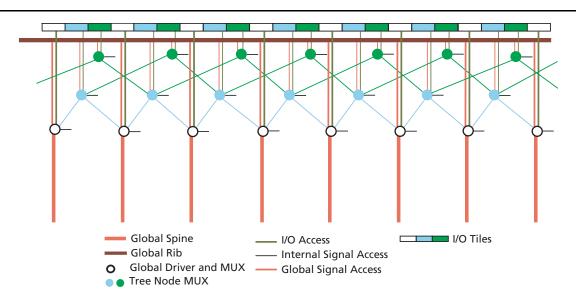

The high-performance VersaNet global networks are low-skew, high-fanout nets that are accessible from external pins or from internal logic (Figure 2-8 on page 2-8). These nets are typically used to distribute clocks, resets, and other high-fanout nets requiring minimum skew. The VersaNet networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically with signals accessing every input on all VersaTiles.

**Note:** Input to the core cell for the D-flip-flop set and reset is only available via the VersaNet global network connection.

Figure 2-5 • Ultra-Fast Local Lines Connected to the Eight Nearest Neighbors

Figure 2-6 • Efficient Long-Line Resources

2-6 Advanced v0.4

Figure 2-7 • Very-Long-Line Resources

#### **Clock Resources (VersaNets)**

ProASIC3E devices offer powerful and flexible control of circuit timing through the use of analog circuitry. Each chip has six CCCs containing a phase-locked loop (PLL) core, delay lines, phase shifter (0°, 90°, 180°, 270°), clock multiplier/dividers, and all the circuitry needed for the selection and interconnection of inputs to the VersaNet global network. The east and west CCCs each have access to three VersaNet global lines on each side of the chip (six total lines). The CCCs at the four corners each have access to three quadrant global lines on each quadrant of the chip.

#### **Advantages of the VersaNet Approach**

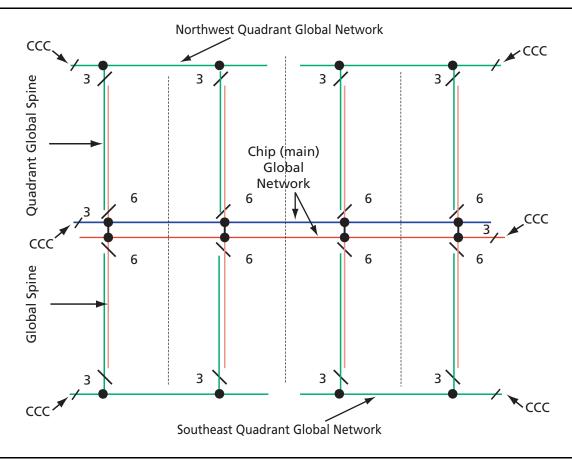

One of the architectural benefits of ProASIC3E is the set of powerful and low-delay VersaNet global networks. ProASIC3E offers six chip (main) global networks that are distributed from the center of the FPGA array (Figure 2-8). In addition, ProASIC3E devices have three regional globals

in each of the four chip quadrants. Each core VersaTile has access to nine global network resources: three quadrant and six chip (main) global networks, and a total of 18 globals on the device. Each of these networks contains spines and ribs that reach all the VersaTiles in the quadrants (Figure 2-9 on page 2-9). This flexible VersaNet global network architecture allows users to map up to 252 different internal/external clocks in a ProASIC3E device. Details on the VersaNet networks are given in Table 2-2 on page 2-9. The flexible use of the ProASIC3E VersaNet global network allows the designer to address several design requirements. User applications that are clock-resourceintensive can easily route external or gated internal clocks using VersaNet global routing networks. Designers can also drastically reduce delay penalties and minimize resource usage by mapping critical, high-fanout nets to the VersaNet global network.

Figure 2-8 • Overview of ProASIC3E VersaNet Global Network

2-8 Advanced v0.4

Figure 2-9 • Global Network Architecture

Table 2-2 • ProASIC3E Globals/Spines/Rows by Device

|                                        | A3PE600 | A3PE1500 | A3PE3000 |

|----------------------------------------|---------|----------|----------|

| Global Clock Networks (Trees)*         | 9       | 9        | 9        |

| Clock Spines/Trees                     | 12      | 20       | 28       |

| Total Spines                           | 108     | 180      | 252      |

| VersaTiles in Each Top or Bottom Spine | 1,120   | 1,888    | 2,656    |

| Total VersaTiles                       | 13,824  | 38,400   | 75,264   |

| Rows in Each Top or Bottom Spine       | 36      | 60       | 84       |

**Note:** \*There are six chip (main) globals and three globals per quadrant.

#### **VersaNet Global Networks and Spine Access**

The ProASIC3E architecture contains a total of 18 segmented global networks that can access the VersaTiles, SRAM memory, and I/O tiles on the ProASIC3E device. There are nine global network resources in each device quadrant: three quadrant globals and six chip (main) global networks. Each device has a total of 18 globals. These VersaNet global networks offer fast, low-skew routing resources for high-fanout nets, including clock signals. In addition, these highly-segmented global networks offer users the flexibility to create low-skew local networks using spines for up to 252 internal/external clocks (in an A3PE3000 device) or other high-fanout nets in ProASIC3E devices. Optimal usage of these low-skew networks can result in significant improvement in design performance on ProASIC3E devices.

The nine spines available in a vertical column reside in global networks with two separate regions of scope: the quadrant global network, which has three spines, and the chip (main) global network, which has six spines. Note that there are three quadrant spines in each quadrant of the device. There are four quadrant global network regions per device (Figure 2-9 on page 2-9).

The spines are the vertical branches of the global network tree, shown in Figure 2-10 on page 2-11. Each spine in a vertical column of a chip (main) global network is further divided into two equal-length spine segments: one in the top and one in the bottom half of the die.

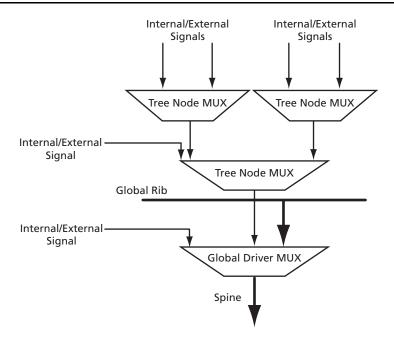

Each spine and its associated ribs cover a certain area of the ProASIC3E device (the "scope" of the spine; see Figure 2-8 on page 2-8). Each spine is accessed by the dedicated global network MUX tree architecture, which defines how a particular spine is driven—either by the signal on the global network from a CCC, for example, or another net defined by the user (Figure 2-11 on page 2-12). Quadrant spines can be driven from user I/Os on the north and south sides of the die. The ability to drive spines in the quadrant global networks can have a significant effect on system performance for high-fanout inputs to a design.

Details of the chip (main) global network spine-selection MUX are presented in Figure 2-11 on page 2-12. The spine drivers for each spine are located in the middle of the die.

Quadrant spines are driven from a north or south rib. Access to the top and bottom ribs is from the corner CCC or from the I/O on the north and south sides of the device.

For details on using spines in ProASIC3E devices, see the Actel application note *Using Global Resources in Actel ProASIC3/E Devices*.

2-10 Advanced v0.4

Figure 2-10 • Spines in a Global Clock Tree Network

# **Clock Aggregation**

Clock aggregation allows for multi-spine clock domains. A MUX tree provides the necessary flexibility to allow long lines or I/Os to access domains of one, two, or four global spines. Signal access to the clock aggregation system is achieved through long-line resources in the central rib, and also through local resources in the north and south ribs, allowing I/Os to directly feed into the clock system. As Figure 2-12 indicates, this access system is contiguous.

There is no break in the middle of the chip for the north and south I/O VersaNet access. This is different from the quadrant clocks, located in these ribs, which only reach the middle of the rib. Refer to the *Using Global Resources in Actel ProASIC3/E Devices* application note.

Figure 2-11 • Spine Selection MUX of Global Tree

Figure 2-12 • Clock Aggregation Tree Architecture

2-12 Advanced v0.4

### **Clock Conditioning Circuits**

#### **Overview of Clock Conditioning Circuitry**

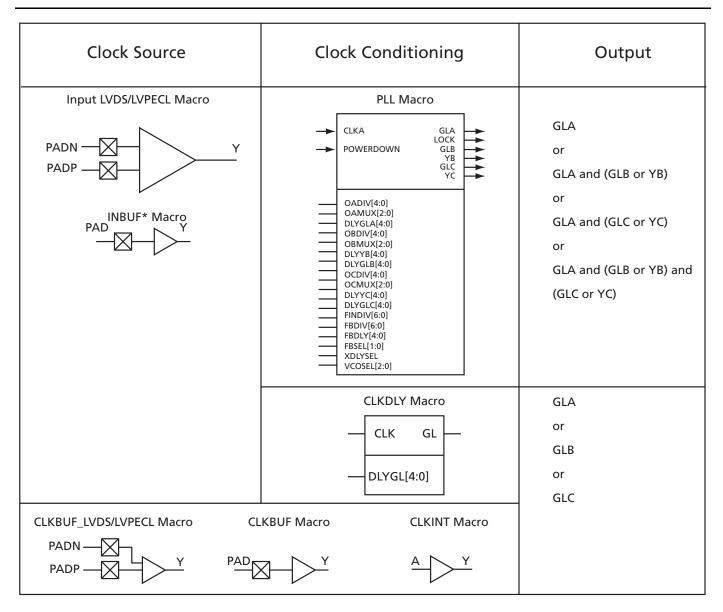

In ProASIC3E devices, the clock conditioning circuits (CCCs) are used to implement frequency division, frequency multiplication, phase shifting, and delay operations.

The CCCs are available in six chip locations – each of the four chip corners and in the middle of the east and west chip sides.

Each CCC can implement up to three independent global buffers (with or without programmable delay), or a PLL function (programmable frequency division/multiplication, phase shift, and delays) with up to three global outputs. Unused global outputs of a PLL can be used to implement independent global buffers, up to a maximum of three global outputs for a given CCC.

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, and CLKC-GLC) of a given CCC.

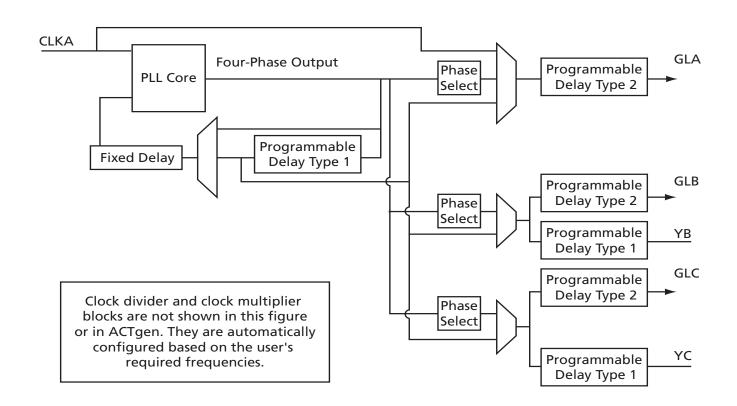

A PLL macro uses the CLKA CCC input to drive its reference clock. It uses the GLA and optionally the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global outputs cannot be reused if the YB (or YC) outputs are used (Figure 2-13 on page 2-14). Refer to the "PLL Macro" section on page 2-15 for more information.

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- Three dedicated single-ended I/Os using a hardwired connection

- Two dedicated differential I/Os using a hardwired connection

- The FPGA core

The CCC block is fully configurable, either via Flash configuration bits set in the programming bitstream or through an asynchronous interface. This asynchronous interface is dynamically accessible from inside the ProASIC3E device to permit parameter changes (such as divide ratios) during device operation. To increase the versatility and flexibility of the clock conditioning system, the CCC configuration is determined either by the user during the design process, with configuration data being stored in Flash memory as part of the device programming procedure, or by writing data into a dedicated shift register during normal device operation. This latter mode allows the user to dynamically reconfigure the CCC without the need for core programming. The shift register is accessed through a simple serial interface. Refer to the UJTAG Applications in ProASIC3/E Device application note and the "CCC Electrical Specifications" section on page 2-18 for more information.

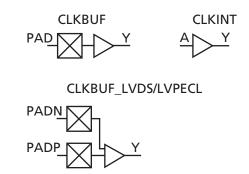

#### **Global Buffers with No Programmable Delays**

The CLKBUF and CLKBUF\_LVPECL/LVDS macros are composite macros that include an I/O macro driving a global buffer, which uses a hardwired connection.

The CLKBUF, CLKBUF\_LVPECL/LVDS, and CLKINT macros are pass-through clock sources and do not use the PLL or provide any programmable delay functionality.

The CLKINT macro provides a global buffer function driven by the FPGA core.

Many specific CLKBUF macros support the wide variety of single-ended and differential I/O standards supported by ProASIC3E devices. The available CLKBUF macros are described in the *ProASIC3/E Macro Library Guide*.

#### **Global Buffer with Programmable Delay**

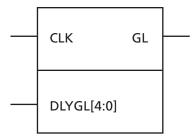

The CLKDLY macro is a pass-through clock source that does not use the PLL, but provides the ability to delay the clock input using a programmable delay. The CLKDLY macro takes the selected clock input and adds a user-defined delay element. This macro generates an output clock phase shift from the input clock.

The CLKDLY macro can be driven by an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

Many specific INBUF macros support the wide variety of single-ended and differential I/O standards supported by the ProASIC3E family. The available INBUF macros are described in the *ProASIC3IE Macro Library Guide*.

The CLKDLY macro can be driven directly from the FPGA core.

The CLKDLY macro can also be driven from an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate from the hardwired I/O connection described earlier.

The visual CLKDLY configuration in the ACTgen part of the Libero IDE and Designer tools allows the user to select the desired amount of delay, and configures the delay elements appropriately. ACTgen also allows the user to select where the input clock is coming from. ACTgen will automatically instantiate the special macro, PLLINT, when needed.

#### Notes:

- 1. Visit the Actel website for future application notes concerning dynamic PLL reconfiguration. Refer to the "PLL Macro" section on page 2-15 for signal descriptions.

- 2. Refer to the ProASIC3/E Macro Library Guide for more information.

- 3. Many specific INBUF macros support the wide variety of single-ended and differential I/O standards supported by the ProASIC3E family. The available INBUF macros are described in the ProASIC3/E Macro Library Guide.

Figure 2-13 • ProASIC3E CCC Options

2-14 Advanced v0.4

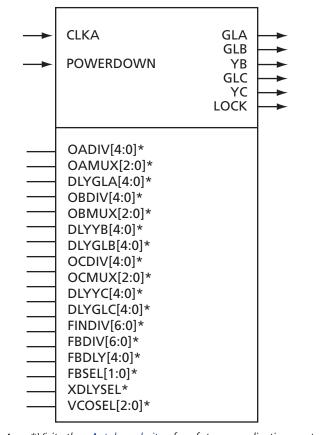

#### **PLL Macro**

The PLL functionality of the clock conditioning block is supported by the PLL macro. Note that the PLL macro reference clock uses the CLKA input of the CCC block, which is only accessible from the global A[0:2] package pins. Refer to Figure 2-14 on page 2-16 for more information.

The PLL macro provides five derived clocks (three independent) from a single reference clock. The PLL macro also provides power-down input and lock output signals. See Figure 2-16 on page 2-17 for more information.

#### Inputs:

- CLKA: selected clock input

- Powerdown (active low): disables PLLs. The default state is Powerdown On (active low).

#### Outputs:

- Lock: indicates that PLL output has locked on the input reference signal

- GLA, GLB, GLC: outputs to respective global networks

- YB, YC: allows output from the CCC to be routed back to the FPGA core

As previously described, the PLL allows up to five flexible and independently-configurable clock outputs. Figure 2-18 on page 2-19 illustrates the various clock output options and delay elements.

As illustrated, the PLL supports three distinct output frequencies from a given input clock. Two of these (GLB and GLC) can be routed to the B and C global network access, respectively, and/or routed to the device core (YB and YC).

There are five delay elements to support phase control on all five outputs (GLA, GLB, GLC, YB, and YC).

There is also a delay element in the feedback loop that can be used to advance the clock relative to the reference clock.

The PLL macro reference clock can be driven by an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

The PLL macro reference clock can be driven by an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

The PLL macro reference clock can be driven directly from the FPGA core.

The PLL macro reference clock can also be driven from an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate from the hardwired I/O connection described earlier.

The visual PLL configuration in ACTgen, associated with the Libero IDE and Designer tools, will derive the necessary internal divider ratios based on the input frequency and desired output frequencies selected by the user. ACTgen also allows the user to select the various delays and phase shift values necessary to adjust the phases between the reference clock (CLKA) and the derived clocks (GLA, GLB, GLC, YB and YC). ACTgen also allows the user to select where the input clock is coming from. ACTgen automatically instantiates the special macro, PLLINT, when needed.

GAA[0:2]: GA represents global in the northwest corner

#### Notes:

- 1. Represents the global input pins. Globals have direct access to the clock conditioning block and are not routed via the FPGA fabric. Refer to the "User I/O Naming Convention" on page 2-49 for more information.

- Instantiate the routed clock source input as follows:

a) Connect the output of a logic element to the clock input of PLL, CLKDLY, or CLKINT macro.

b) Do not place a clock source I/O (INBUF or INBUF\_LVPECL/LVDS) in a relevant global pin location.

Figure 2-14 • Clock Input Sources Including CLKBUF, CLKBUF\_LVDS/LVPECL, and CLKINT

Figure 2-15 • CLKBUF and CLKINT

2-16 Advanced v0.4

Table 2-3 • Available Selections of I/O Standards within CLKBUF and CLKBUF\_LVDS/LVPECL Macros

| CLKBUF Macros    |

|------------------|

| CLKBUF_LVCMOS5   |

| CLKBUF_LVCMOS33* |

| CLKBUF_LVCMOS25  |

| CLKBUF_LVCMOS18  |

| CLKBUF_LVCMOS15  |

| CLKBUF_PCI       |

| CLKBUF_PCIX      |

| CLKBUF_GTL25     |

| CLKBUF_GTL33     |

| CLKBUF_GTLP25    |

| CLKBUF_GTLP33    |

| CLKBUF_HSTL_I    |

| CLKBUF_HSTL_II   |

| CLKBUF_SSTL3_I   |

| CLKBUF_SSTL3_II  |

| CLKBUF_SSTL2_I   |

| CLKBUF_SSTL2_II  |

| CLKBUF_LVDS      |

| CLKBUF_LVPECL    |

|                  |

**Note:** \*By default, the CLKBUF macro uses the 3.3 V LVTTL I/O technology. For more details, refer to the ProASIC3/E Macro Library Guide.

**Note:** \*Visit the Actel website for future application notes concerning the dynamic PLL.

Figure 2-16 • CCC/PLL Macro

#### **CLKDLY**

**Note:** The CLKDLY macro uses programmable delay element type 2.

Figure 2-17 • CLKDLY

# **CCC Electrical Specifications**

Timing Characteristics

*Table 2-4* • **ProASIC3E CCC/PLL Specification**

| Parameter                                                          | Min.                        | Тур.          | Max.                         | Unit |

|--------------------------------------------------------------------|-----------------------------|---------------|------------------------------|------|

| Clock Conditioning Circuitry Input Frequency f <sub>IN_CCC</sub>   | 1.5                         |               | 350                          | MHz  |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub> | 0.75                        |               | 350                          | MHz  |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>      |                             | 160           |                              | ps   |

| Number of Programmable Values in Each Programmable Delay Block     |                             |               | 32                           |      |

| Input Period Jitter                                                |                             |               | 1.5                          | ns   |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | Max Pe                      | ak-to-Peak Pe | riod Jitter                  |      |

|                                                                    | 1 Global<br>Network<br>Used |               | 3 Global<br>Networks<br>Used |      |

| 0.75 MHz to 24 MHz                                                 | 0.50%                       |               | 0.70%                        |      |

| 24 MHz to 100 MHz                                                  | 1.00%                       |               | 1.20%                        |      |

| 100 MHz to 250 MHz                                                 | 1.75%                       |               | 2.00%                        |      |

| 250 MHz to 350 MHz                                                 | 2.50%                       |               | 5.60%                        |      |

| Acquisition Time                                                   |                             |               | 150                          | μs   |

| Output Duty Cycle                                                  | 48.5                        |               | 51.5                         | %    |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>         | 0.6                         |               | 5.56                         | ns   |

| Delay Range in Block: Programmable Delay 2 1, 2                    | 0.025                       |               | 5.56                         | ns   |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                  |                             | 2.2           |                              | ns   |

#### Notes:

2-18 Advanced v0.4

<sup>1.</sup> This delay is a function of voltage and temperature. See Table 3-6 on page 3-4 for deratings.

<sup>2.</sup>  $T_J = 25$ °C,  $V_{CC} = 1.5 V$

#### **CCC Physical Implementation**

The CCC circuit is composed of the following (Figure 2-18):

- PLL core

- Three phase selectors

- Six programmable delays and one fixed delay that advance/delay phase

- Five programmable frequency dividers that provide frequency multiplication/division (not shown in Figure 2-18, because they are automatically configured based on the user's required frequencies)

- One dynamic shift register that provides CCC dynamic reconfiguration capability

#### **CCC Programming**

The clock conditioning circuit block is fully configurable, either via static Flash configuration bits in the array, set by the user in the programming bitstream, or through an asynchronous dedicated shift register dynamically accessible from inside the ProASIC3E device. The dedicated shift register permits parameter changes such as PLL divide ratios and delays during device operation. This latter mode allows the user to dynamically reconfigure the PLL without the need for core programming. The register file is accessed through a simple serial interface. Refer to the *UJTAG Applications in ProASIC3/E Devices* application note for more information.

Note: Refer to the "Clock Conditioning Circuits" section on page 2-13 and Table 2-4 on page 2-18 for signal descriptions.

Figure 2-18 • PLL Block

# **Nonvolatile Memory (NVM)**

#### Overview of User Nonvolatile FlashROM (FROM)

ProASIC3E devices have 1 kbit of on-chip nonvolatile Flash memory that can be read from the FPGA core fabric. The FROM is arranged in 8 banks of 128 bits during programming. The 128 bits in each bank are addressable as 16 bytes during the read back of the FROM from the FPGA core (Figure 2-19).

The FROM can only be programmed via the IEEE1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the 8 128-bit banks can be selectively reprogrammed. The FROM can only be reprogrammed on a bank boundary.

Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FROM supports asynchronous read with a nominal 10 ns access time. The FROM can be read on byte boundaries. The upper 3 bits of the FROM address from the FPGA core define the bank that is being accessed. The lower 4 bits of the FROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

|                         |   | Byt | e Nu | ımbe | er in | Ban | ık |   | 4 LSB of ADDR (READ) |   |   |   |   |   |   |   |   |

|-------------------------|---|-----|------|------|-------|-----|----|---|----------------------|---|---|---|---|---|---|---|---|

|                         |   | 15  | 14   | 13   | 12    | 11  | 10 | 9 | 8                    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Ва                      | 7 |     |      |      |       |     |    |   |                      |   |   |   |   |   |   |   |   |

| Bank Number<br>ADDR (RI | 6 |     |      |      |       |     |    |   |                      |   |   |   |   |   |   |   |   |

| Vun                     | 5 |     |      |      |       |     |    |   |                      |   |   |   |   |   |   |   |   |

| າbe<br>₹ (R             | 4 |     |      |      |       |     |    |   |                      |   |   |   |   |   |   |   |   |

| <del>`</del>            | 3 |     |      |      |       |     |    |   |                      |   |   |   |   |   |   |   |   |

| 3 M<br>D)               | 2 |     |      |      |       |     |    |   |                      |   |   |   |   |   |   |   |   |

| MSB (                   | 1 |     |      |      |       |     |    |   |                      |   |   |   |   |   |   |   |   |

| of                      | 0 |     |      |      |       |     |    |   |                      |   |   |   |   |   |   |   |   |

Figure 2-19 • FROM Architecture

2-20 Advanced v0.4

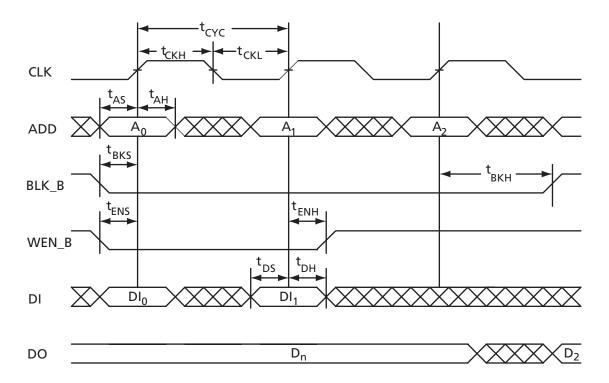

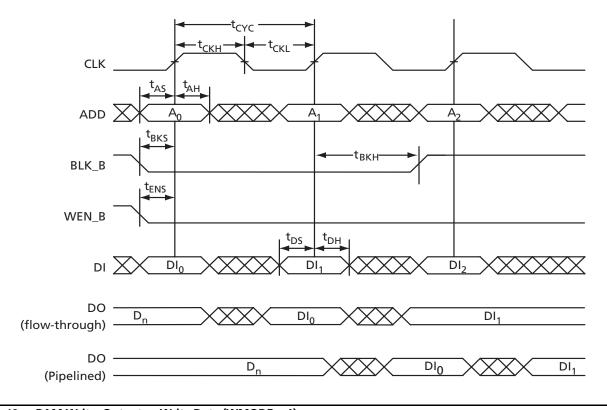

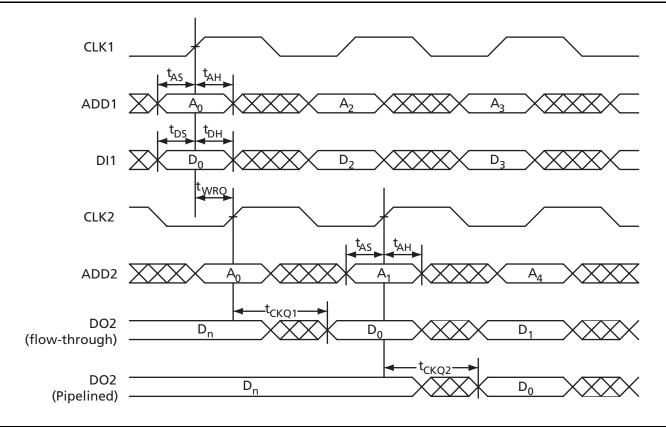

#### SRAM and FIFO

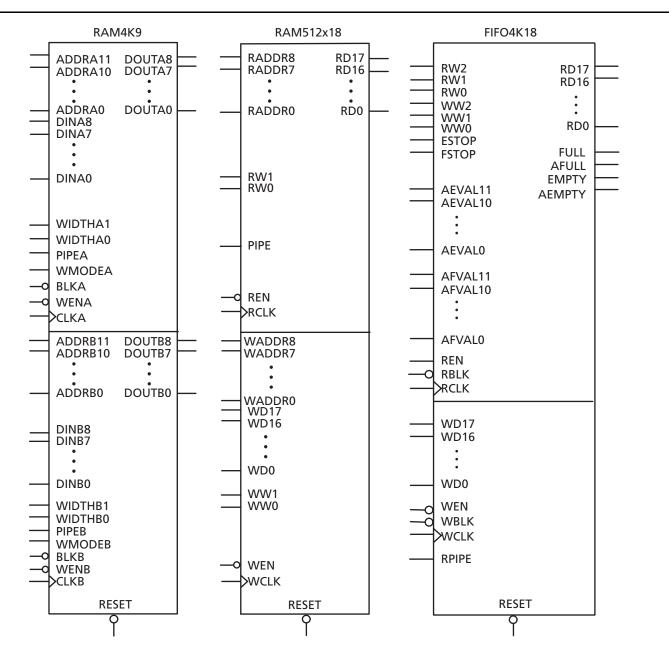

ProASIC3E devices have embedded SRAM blocks along the north side of the device. To meet the needs of high-performance designs, the memory blocks operate strictly in synchronous mode for both read and write operations. The read and write clocks are completely independent, and each may operate at any desired frequency less than or equal to 350 MHz.

- 4kx1, 2kx2, 1kx4, 512x9 (dual-port RAM two read, two write or one read, one write)

- 512x9, 256x18 (two-port RAM one read and one write)

- Sync write, sync pipelined / nonpipelined read

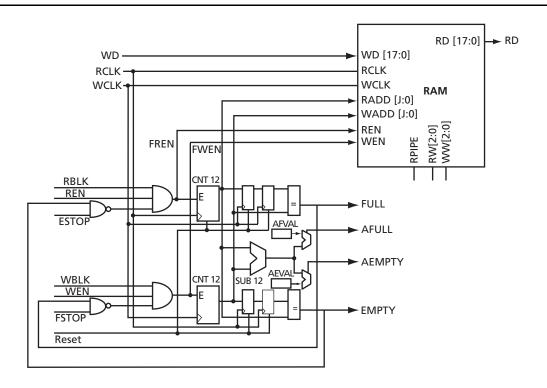

The ProASIC3E memory block includes dedicated FIFO control logic to generate internal addresses and external flag logic (Full, Empty, AFULL, AEMPTY). Block diagrams of the memory modules are illustrated in Figure 2-20 on page 2-22.

During RAM operation, addresses are sourced by the user logic and the FIFO controller is ignored. In FIFO mode, the internal addresses are generated by the FIFO controller and routed to the RAM array by internal MUXes. Refer to Figure 2-21 on page 2-23 for more information about the implementation of the embedded FIFO controller.

The ProASIC3E architecture enables the read and write sizes of RAMs to be organized independently, allowing for bus conversion. For example, the write side size can be set to 256x18 and the read size to 512x9.

Both the write width and read width for the RAM blocks can be specified independently with the WW (write width) and RW (read width) pins. The different DxW configurations are: 256x18, 512x9, 1kx4, 2kx2, and 4kx1.

Refer to the allowable RW and WW values supported for each of the RAM macro types in Table 2-5 on page 2-24.

When widths of one, two, and four are selected, the ninth bit is unused. For example, when writing nine-bit values and reading four-bit values, only the first four bits and the second four bits of each nine-bit value are addressable for read operations. The ninth bit is not accessible.

Conversely, when writing four-bit values and reading nine-bit values, the ninth bit of a read operation will be undefined. The RAM blocks employ little-endian byte order for read and write operations.

Figure 2-20 • Supported Basic RAM Macros

2-22 Advanced v0.4

Figure 2-21 • ProASIC3E RAM Block with Embedded FIFO Controller

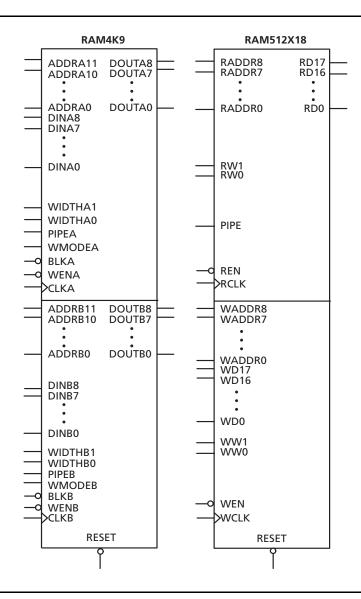

#### **Signal Descriptions for RAM4K9**

The following signals are used to configure the RAM4K9 memory element:

#### WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 2-5).

Table 2-5 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA1, WIDTHA0 | WIDTHB1, WIDTHB0 | DxW   |

|------------------|------------------|-------|

| 00               | 00               | 4kx1  |

| 01               | 01               | 2kx2  |

| 10               | 10               | 1kx4  |

| 11               | 11               | 512x9 |

**Note:** The aspect ratio settings are constant and cannot be changed on-the-fly.

#### **BLKA and BLKB**

These signals are active low and will enable the respective ports when asserted. When a BLKx signal is deasserted, that port's outputs hold the previous value.

#### WENA and WENB

These signals switch the RAM between read and write modes for the respective ports. A Low on these signals indicates a write operation, and a High indicates a read.

#### **CLKA and CLKB**

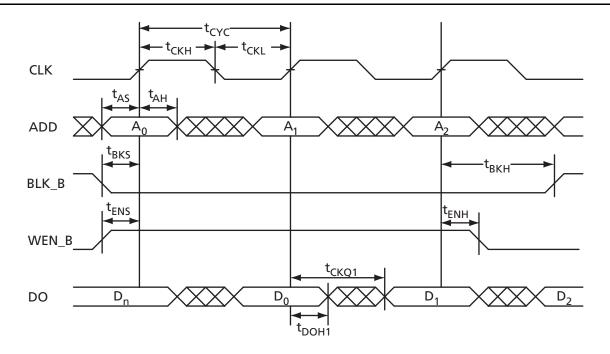

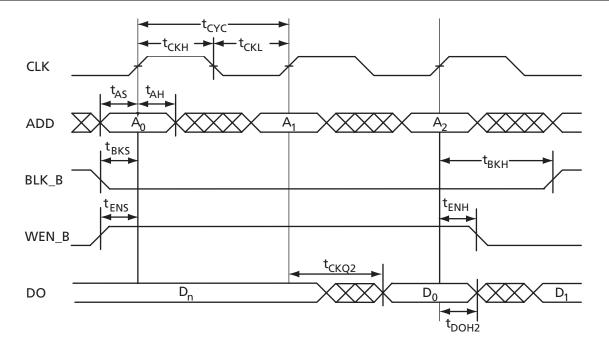

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### **PIPEA** and **PIPEB**

These signals are used to specify pipelined read on the output. A Low on PIPEA and/or PIPEB indicates a nonpipelined read and the data appears on the corresponding output in the same clock cycle. A High indicates a pipelined read and data appears on the corresponding output in the next clock cycle.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when RAM is in the write mode. A Low on these signals makes the output retain data from the previous read. A High indicates pass-through behavior where the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

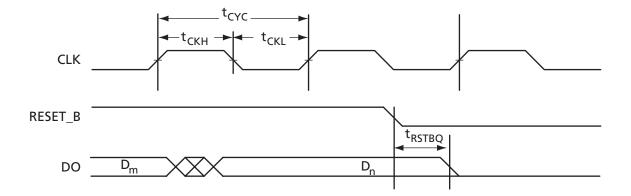

#### **RESET**

This active low signal resets the output to zero when asserted. It does not reset the contents of the memory.

#### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4k is specified, the unused high-order bits must be grounded (Table 2-6).

Table 2-6 • Address Pins Unused/Used for Various Supported Bus Widths

|       | ADDRx   |        |

|-------|---------|--------|

| DxW   | Unused  | Used   |

| 4kx1  | None    | [11:0] |

| 2kx2  | [11]    | [10:0] |

| 1kx4  | [11:10] | [9:0]  |

| 512x9 | [11:9]  | [8:0]  |

**Note:** The "x" in ADDRx implies A or B.

#### **DINA and DINB**

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 2-7).

#### **DOUTA and DOUTB**

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 2-7). The output data on unused pins is undefined.

Table 2-7 • Unused/Used Input and Output Data Pins for Various Supported Bus Widths

|       | DINx/DOUTx |       |

|-------|------------|-------|

| DxW   | Unused     | Used  |

| 4kx1  | [8:1]      | [0]   |

| 2kx2  | [8:2]      | [1:0] |

| 1kx4  | [8:4]      | [3:0] |

| 512x9 | None       | [8:0] |

**Note:** The "x" in DINx or DOUTx implies A or B.

2-24 Advanced v0.4

### Signal Descriptions for RAM512X18

RAM512X18 has slightly different behavior than the RAM4K9, as it has dedicated read and write ports.

#### WW and RW

These signals enable the RAM to be configured in one of the two allowable aspect ratios (Table 2-8).

Table 2-8 • Aspect Ratio Settings for WW[1:0]

| ww1, wwo | RW1, RW0 | DxW      |  |  |

|----------|----------|----------|--|--|

| 01       | 01       | 512x9    |  |  |

| 10       | 10       | 256x18   |  |  |

| 00, 11   | 00, 11   | Reserved |  |  |

#### WD and RD

These are the input and output data signals, and they are 18 bits wide. When a 512x9 aspect ratio is used for write, WD[17:9] are unused and must be grounded. If this aspect ratio is used for read, then RD[17:9] are undefined.

#### WADDR and RADDR

These are read and write addresses, and they are nine bits wide. When the 256x18 aspect ratio is used for write and/or read, WADDR[8] and/or RADDR[8] are/is unused and must be grounded.

#### WCLK and RCLK

These signals are the write and read clocks, respectively. They are both active high.

#### WEN and REN

These signals are the write and read enables, respectively. They are both active low by default. These signals can be configured as active high.

#### RESET

This active low signal resets the output to zero when asserted. It does not reset the contents of the memory.

#### PIPE

This signal is used to specify pipelined read on the output. A Low on PIPE indicates a nonpipelined read and the data appears on the output in the same clock cycle. A High indicates a pipelined read and data appears on the output in the next clock cycle.

#### Clocking

The dual-port SRAM blocks are only clocked on the rising edge. ACTgen allows falling-edge triggered clocks by adding inverters to the netlist, hence achieving dual-port SRAM blocks that are clocked on either edge (rising or falling). For dual-port SRAM, each port can be clocked on either edge and/or by separate clocks by port.

ProASIC3E devices support inversion (bubble pushing) throughout the FPGA architecture, including the clock input to the SRAM modules. Inversions added to the SRAM clock pin on the design schematic or in the HDL code will be automatically accounted for during design compile without incurring additional delay in the clock path.

The two-port SRAM can be clocked on the rising edge or falling edge of the WCLK and RCLK.

If negative-edge RAM and FIFO clocking is selected for memory macros, clock edge inversion management (bubble pushing) is automatically used within the ProASIC3E development tools, without performance penalty.

#### **Modes of Operation**

There are two read modes and one write mode:

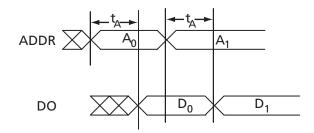

- Read Nonpipelined (synchronous one clock edge): In the standard read mode, new data is driven onto the RD bus in the same clock cycle following RA and REN valid. The read address is registered on the read port clock active edge and data appears at RD after the RAM access time. Setting PIPE to OFF enables this mode.

- Read Pipelined (synchronous two clock edges):

The pipelined mode incurs an additional clock delay from the address to the data but enables operation at a much higher frequency. The read address is registered on the read port active clock edge, and the read data is registered and appears at RD after the second read clock edge. Setting the PIPE to ON enables this mode.

- Write (synchronous one clock edge): On the write clock active edge, the write data is written into the SRAM at the write address when WEN is high. The setup times of the write address, write enables, and write data are minimal with respect to the write clock. Write and read transfers are described with timing requirements in the "DDR Module Specifications" section on page 3-55.

#### **RAM Initialization**

Each SRAM block can be individually initialized on power-up by means of the JTAG port using the UJTAG mechanism (refer to the "JTAG 1532" section on page 2-53 and the *ProASIC3/E SRAM/FIFO Blocks* application note). The shift register for a target block can be selected and loaded with the proper bit configuration to enable serial loading. The 4,608 bits of data can be loaded in a single operation.

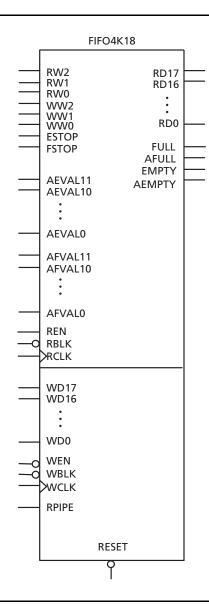

### Signal Descriptions for FIFO4K18

The following signals are used to configure the FIFO4K18 memory element:

#### WW and RW

These signals enable the FIFO to be configured in one of the five allowable aspect ratios (Table 2-9).

Table 2-9 • Aspect Ratio Settings for WW[2:0]

| WW2, WW1, WW0 | RW2, RW1, RW0 | DxW      |

|---------------|---------------|----------|

| 000           | 000           | 4kx1     |

| 001           | 001           | 2kx2     |

| 010           | 010           | 1kx4     |

| 011           | 011           | 512x9    |

| 100           | 100           | 256x18   |

| 101, 110, 111 | 101, 110, 111 | Reserved |

#### WBLK and RBLK

These signals are active low and will enable the respective ports when low. When the RBLK signal is high, that port's outputs hold the previous value.

#### WEN and REN

Read and write enables. WEN is active low and REN is active high by default. These signals can be configured as active high or low.

#### WCLK and RCLK

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### **RPIPE**

This signal is used to specify pipelined read on the output. A Low on RPIPE indicates a nonpipelined read and the data appears on the output in the same clock cycle. A High indicates a pipelined read and data appears on the output in the next clock cycle.

#### RESET

This active low signal resets the output to zero when asserted. It resets the FIFO counters. It also sets all the RD pins low, the Full and AFULL pins low, and the Empty and AEMPTY pins high (Table 2-10).

#### WD

This is the input data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. When a data width less than 18 is specified, unused higher-order signals must be grounded (Table 2-10).

#### RD

This is the output data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. Like the WD bus, highorder bits become unusable if the data width is less than 18. The output data on unused pins is undefined (Table 2-10).

Table 2-10 • Input Data Signal Usage for Different Aspect

Ratios

| DxW    | WD/RD Unused       |

|--------|--------------------|

| 4kx1   | WD[17:1], RD[17:1] |

| 2kx2   | WD[17:2], RD[17:2] |

| 1kx4   | WD[17:4], RD[17:4] |

| 512x9  | WD[17:9], RD[17:9] |

| 256x18 | -                  |

#### **ESTOP, FSTOP**

ESTOP is used to stop the FIFO read counter from further counting once the FIFO is empty (i.e., the Empty flag goes high). A High on this signal inhibits the counting.

FSTOP is used to stop the FIFO write counter from further counting once the FIFO is full (i.e., the Full flag goes high). A High on this signal inhibits the counting.

For more information on these signals, refer to the "ESTOP and FSTOP Usage" section on page 2-27.

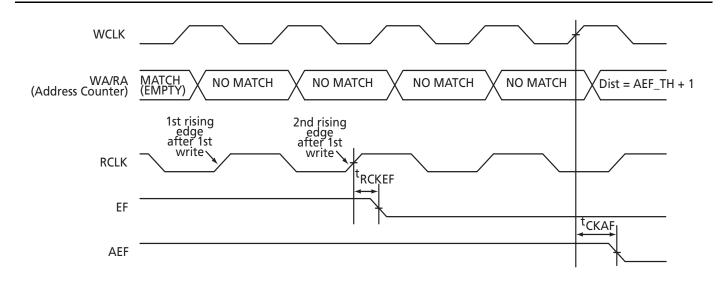

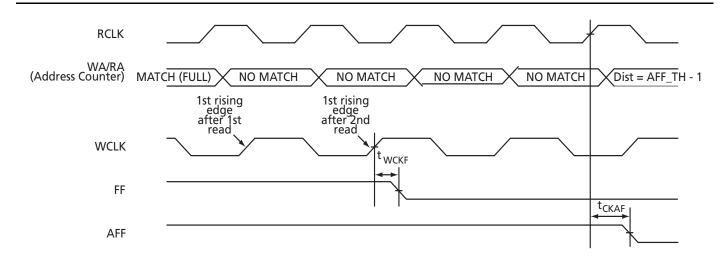

#### **FULL, EMPTY**

When the FIFO is full and no more data can be written, the Full flag asserts high. The Full flag is synchronous to WCLK to inhibit writing immediately upon detection of a full condition and to prevent overflows. Since the write address is compared to a resynchronized (and thus time-delayed) version of the read address, the Full flag will remain asserted until two WCLK active edges after a read operation eliminates the full condition.

When the FIFO is empty and no more data can be read, the Empty flag asserts high. The Empty flag is synchronous to RCLK to inhibit reading immediately upon detection of an empty condition and to prevent underflows. Since the read address is compared to a resynchronized (and thus time delayed) version of the write address, the Empty flag will remain asserted until two RCLK active edges, after a write operation, removes the empty condition.

For more information on these signals, refer to the "FIFO Flag Usage Considerations" section on page 2-27.

#### **AFULL, AEMPTY**

These are programmable flags and will be asserted on the threshold specified by AFVAL and AEVAL, respectively.

When the number of words stored in the FIFO reaches the amount specified by AEVAL while reading, the AEMPTY output will go high. Likewise, when the number of words stored in the FIFO reaches the amount specified by AFVAL while writing, the AFULL output will go high.

#### AFVAL, AEVAL

The AEVAL and AFVAL pins are used to specify the almost-empty and almost-full threshold values, respectively. They are 12-bit signals. For more information on these signals, refer to the "FIFO Flag Usage Considerations" section on page 2-27.

2-26 Advanced v0.4

#### **ESTOP and FSTOP Usage**

The ESTOP pin is used to stop the read counter from counting any further once the FIFO is empty (i.e., the EMPTY flag goes high). Likewise, the FSTOP pin is used to stop the write counter from counting any further once the FIFO is full (i.e., the Full flag goes high).

The FIFO counters in the ProASIC3E device start the count at 0, reach the maximum depth for the configuration (e.g., 511 for a 512x9 configuration), and then restart at 0. An example application for the ESTOP, where the read counter keeps counting, would be writing to the FIFO once and reading the same content over and over without doing another write.

#### **FIFO Flag Usage Considerations**

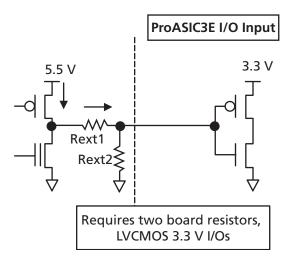

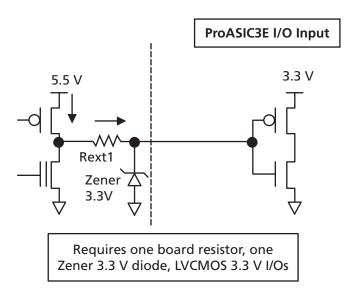

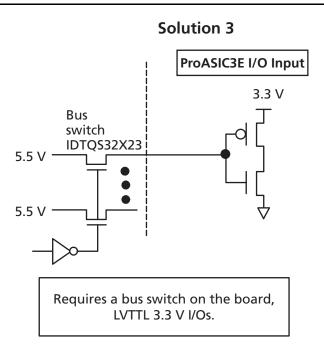

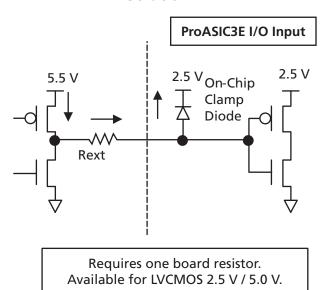

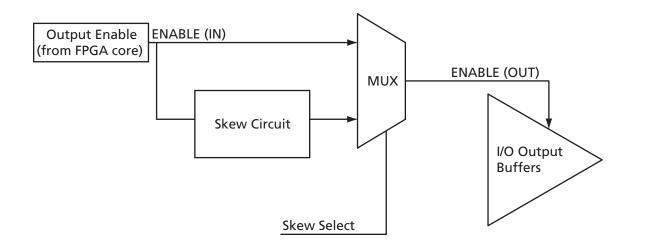

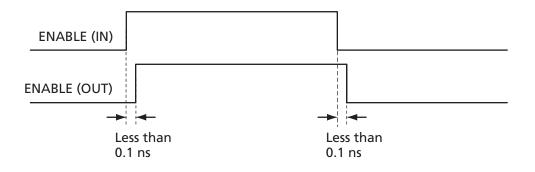

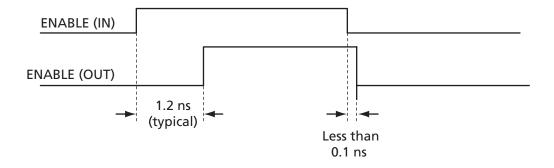

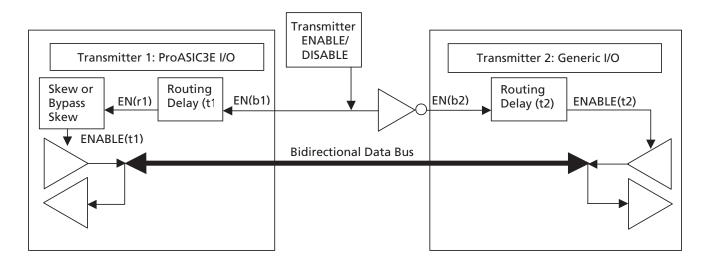

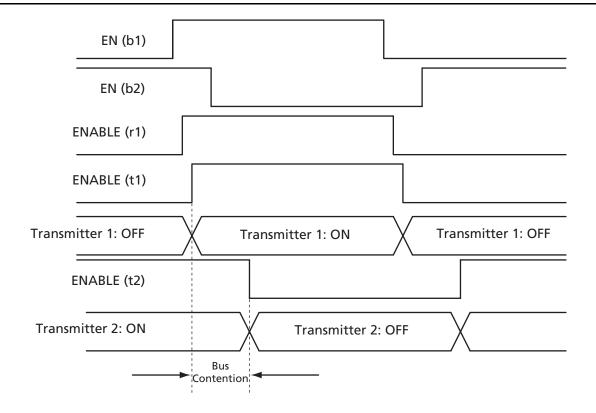

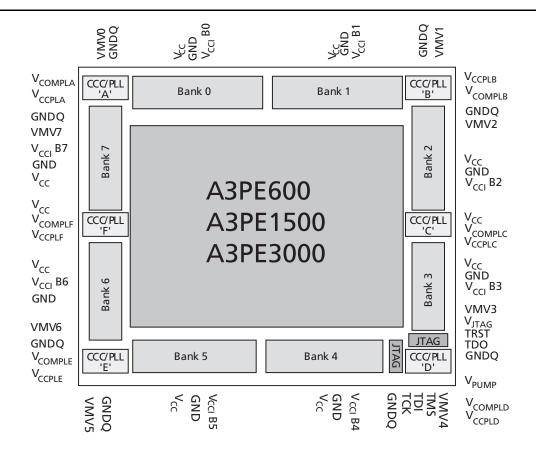

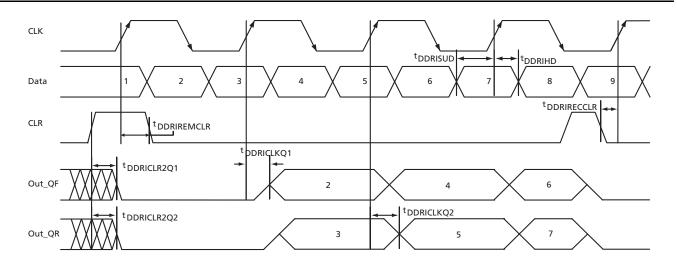

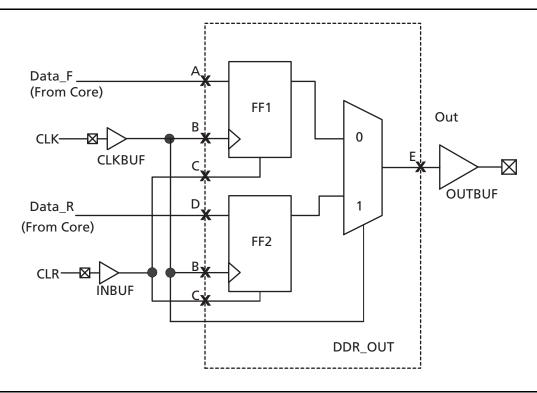

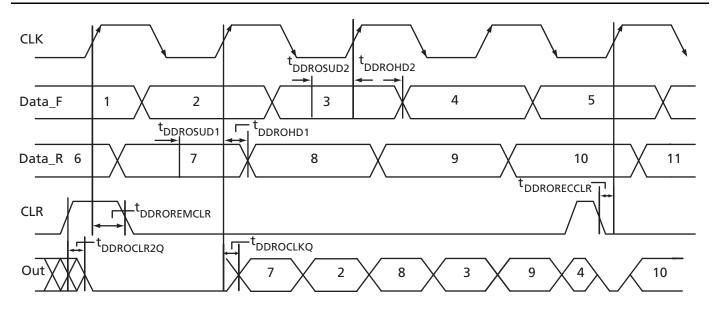

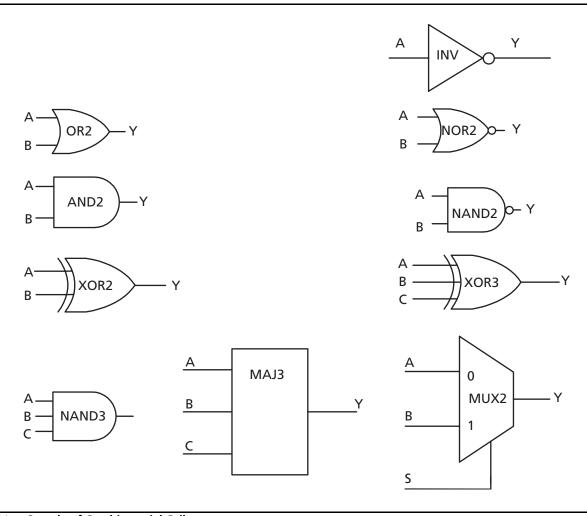

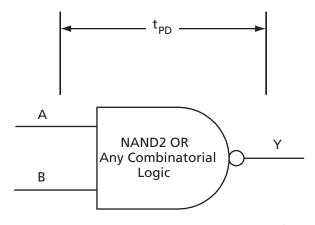

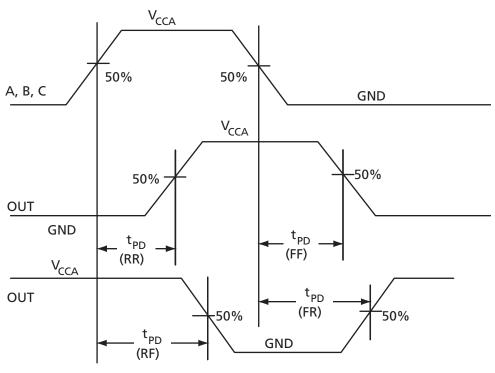

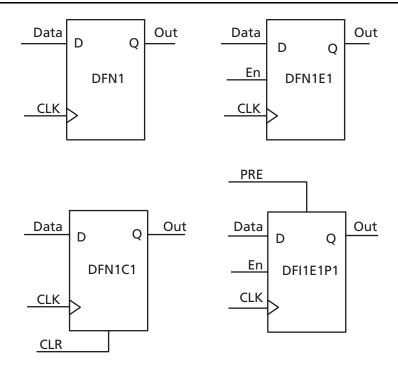

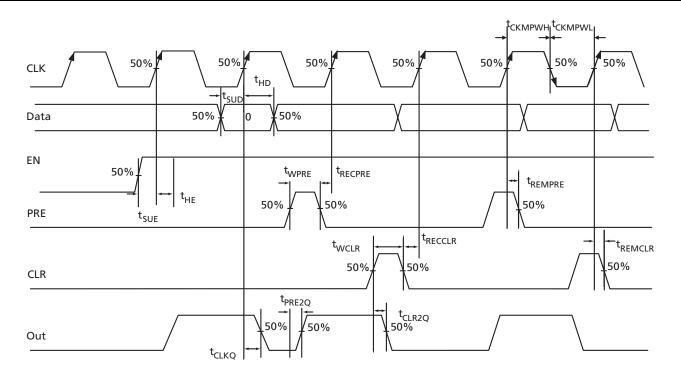

The AEVAL and AFVAL pins are used to specify the 12-bit AEMPTY and AFULL threshold values, respectively. The FIFO contains separate 12-bit write address (WADDR) and read address (RADDR) counters. WADDR is incremented every time a write operation is performed, and RADDR is incremented every time a read operation is performed. Whenever the difference between WADDR and RADDR is greater than or equal to AFVAL, the AFULL output is asserted. Likewise, whenever the difference between WADDR and RADDR is less than or equal to AEVAL, the AEMPTY output is asserted. To handle different read and write aspect ratios, AFVAL and AEVAL are expressed in terms of total data bits instead of total data words. When users specify AFVAL and AEVAL in terms of read or write words, the ACTgen tool translates them into bit addresses and configures these signals automatically. ACTgen configures the AFULL flag, AFULL, to assert when the write address exceeds the read address by at least a predefined value. In a 2kx8 FIFO, for example, a value of 1,500 for AFVAL means that the AFULL flag will be asserted after a write when the difference between the write address and the read address reaches 1.500 (there have been at least 1.500 more writes than reads). It will stay asserted until the difference between the write and read addresses drops below 1,500.